SBVU085 December 2024

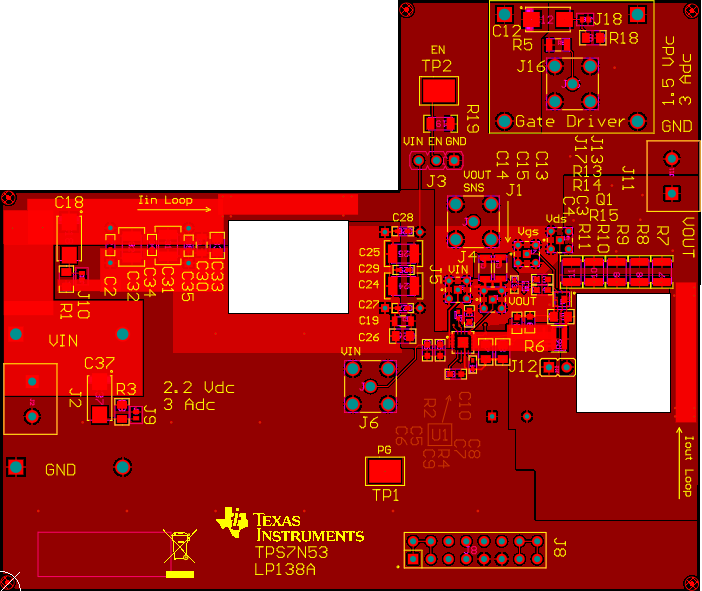

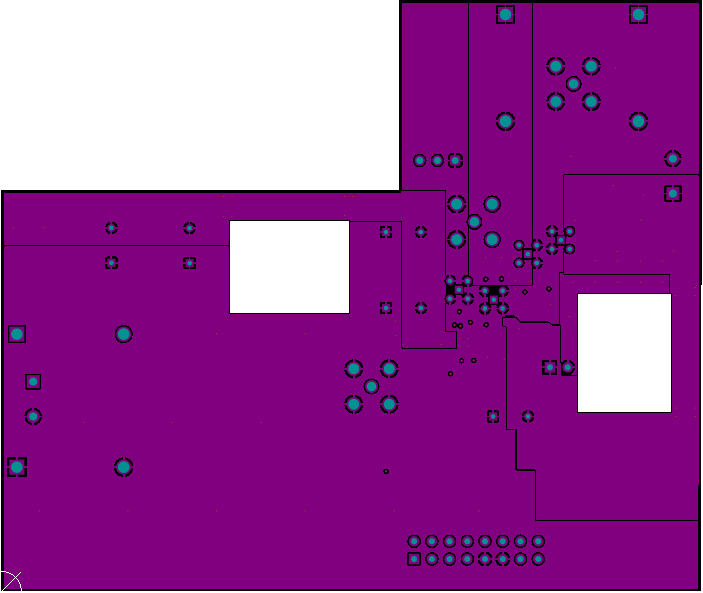

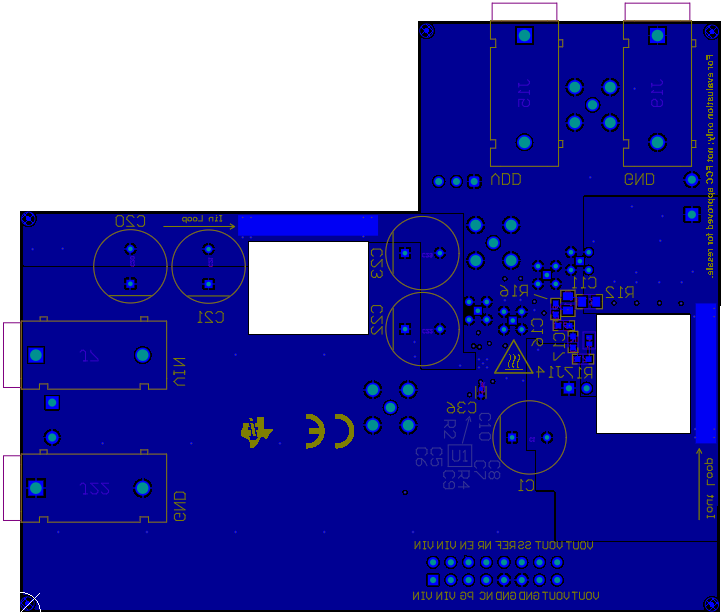

4.2 PCB Layouts

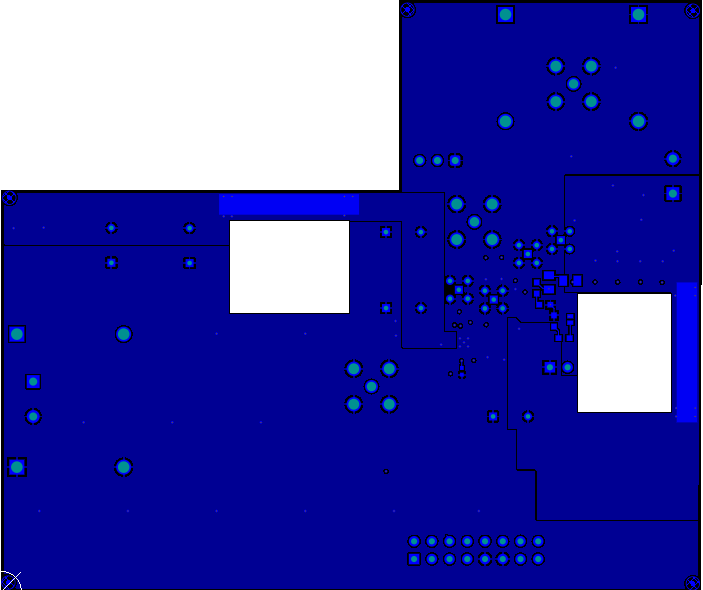

Figure 4-4 Top

Assembly Layer and Silkscreen

Figure 4-4 Top

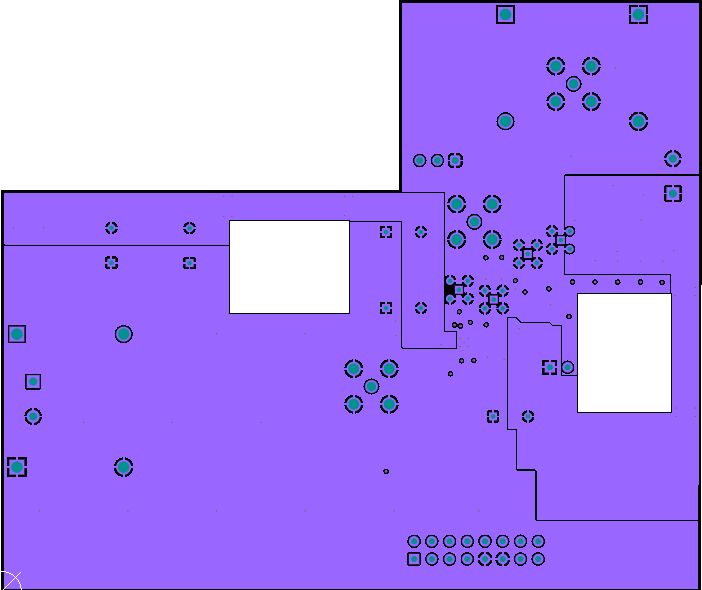

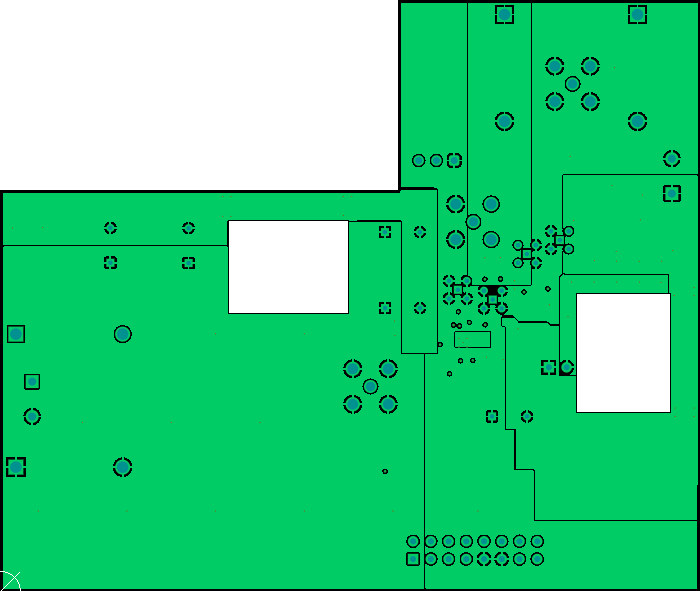

Assembly Layer and Silkscreen Figure 4-6 Layer

2

Figure 4-6 Layer

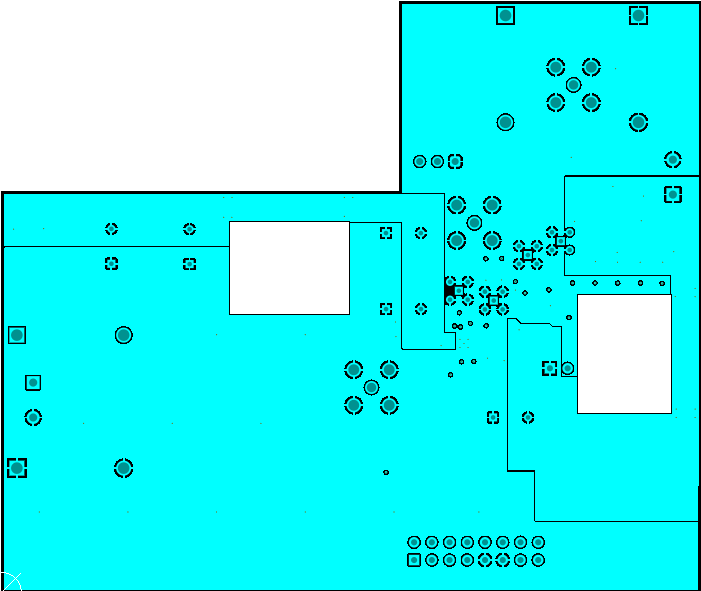

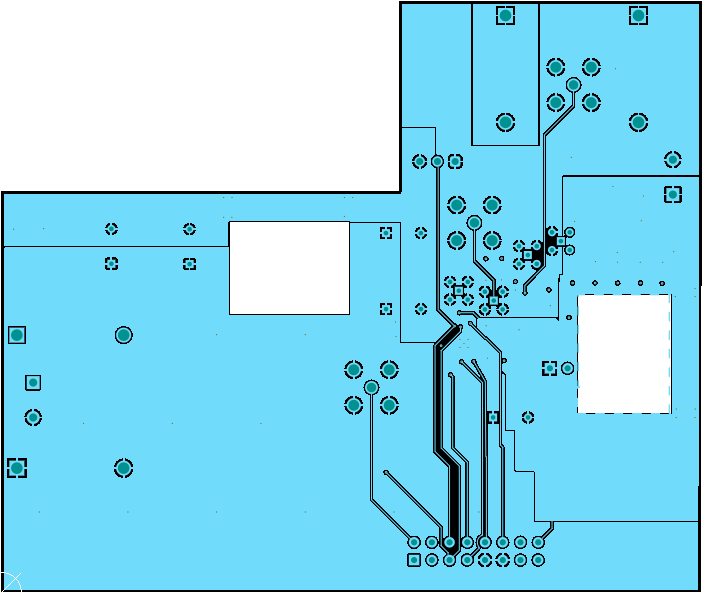

2 Figure 4-8 Layer

4

Figure 4-8 Layer

4 Figure 4-10 Layer

6

Figure 4-10 Layer

6 Figure 4-12 Bottom Layer Routing

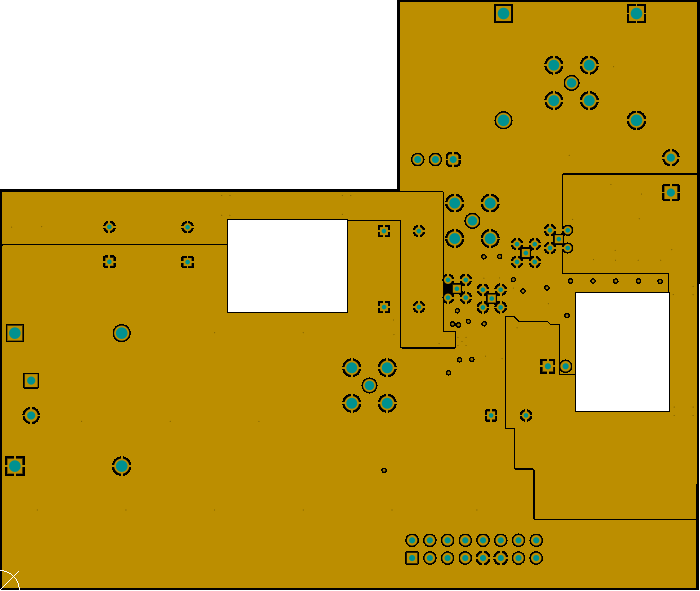

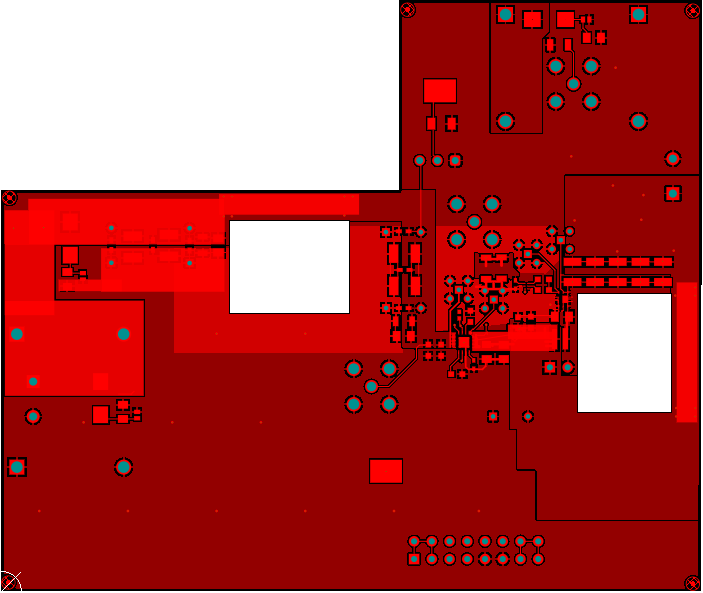

Figure 4-12 Bottom Layer Routing Figure 4-5 Top

Layer Routing

Figure 4-5 Top

Layer Routing Figure 4-7 Layer

3

Figure 4-7 Layer

3 Figure 4-9 Layer

5

Figure 4-9 Layer

5 Figure 4-11 Layer

7

Figure 4-11 Layer

7 Figure 4-13 Bottom Assembly Layer and Silkscreen

Figure 4-13 Bottom Assembly Layer and Silkscreen