SLAAE71 December 2022 MSPM0G1105 , MSPM0G1106 , MSPM0G1107 , MSPM0G1505 , MSPM0G1506 , MSPM0G1507 , MSPM0G3105 , MSPM0G3106 , MSPM0G3107 , MSPM0G3505 , MSPM0G3506 , MSPM0G3507

- Abstract

- Trademarks

- 1Overview

- 2Low-Power Features in PMCU

- 3Low-Power Optimization

- 4Power Consumption Measurement and Evaluation

2.1.1 Power Domains and Power Modes

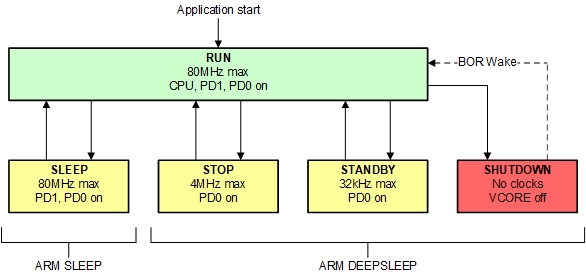

To realize different power levels, two core power domains are provided on the device: PD1 and PD0 and five operating modes (power modes) are provided to optimize the device power decreasing power: RUN, SLEEP, STOP, STANDBY, and SHUTDOWN. Figure 2-1 indicates what domains are available in each operating mode of the device.

Figure 2-1 MSPM0Gxx Operating Modes

Figure 2-1 MSPM0Gxx Operating ModesTable 2-1 gives a more detailed list of the supported functionality in each operating mode. Users can choose the working conditions of the application according to the clock frequency, wake sources, CPU and peripherals requirements.

Abbreviations used in Table 2-1:

EN: The function is enabled in the specified mode.

DIS: The function is disabled in the specified mode, but the function's configuration is retained.

OPT: The function is optional in the specified mode, and remains enabled if configured to be enabled.

NS: The function is not automatically disabled in the specified mode, but its use is not supported.

OFF: The function is powered off in the specified mode, and no configuration information is retained.

| Operating Mode | RUN | SLEEP | STOP | STANDBY | SHUTDOWN | ||||||||

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| RUN0 | RUN1 | RUN2 | SLEEP0 | SLEEP1 | SLEEP2 | STOP0 | STOP1 | STOP2 | STANDBY0 | STANDBY1 | |||

| Oscillators | SYSOSC | EN | EN | DIS | EN | EN | DIS | OPT | EN | DIS | DIS | DIS | OFF |

| LFOSC or LFXT | EN (LFOSC or LFXT) | OFF | |||||||||||

| HFXT | OPT | DIS | DIS | OPT | DIS | DIS | DIS | DIS | DIS | DIS | DIS | OFF | |

| SYSPLL | OPT | DIS | DIS | OPT | DIS | DIS | DIS | DIS | DIS | DIS | DIS | OFF | |

| Clocks | CPUCLK | 80 MHz max | 32 kHz | 32 kHz | DIS | OFF | |||||||

| MCLK to PD1 | 80 MHz max | 32 kHz | 32 kHz | 80 MHz max | 32 kHz |

32 kHz |

DIS |

OFF | |||||

| ULPCLK to PD0 | 40 MHz max | 32 kHz | 32 kHz | 40 MHz max | 32 kHz |

32 kHz |

4 MHz max | 4 MHz | 32 kHz | DIS | OFF | ||

| ULPCLK to TIMG0/1 | 40 MHz max | 32 kHz | 32 kHz | 40 MHz max | 32 kHz | 32 kHz | 4 MHz max | 4 MHz | 32 kHz | OFF | |||

| RTCCLK | 32 kHz | OFF | |||||||||||

| MFCLK | OPT | DIS | OPT | DIS | OPT | DIS | OFF | ||||||

| MFPCLK | OPT | DIS | OPT | DIS | OPT | DIS | OFF | ||||||

| LFCLK | 32 kHz | DIS | OFF | ||||||||||

| LFCLK to TIMG0/1 | 32 kHz | OFF | |||||||||||

| LFCLK Monitor | OPT | OFF | |||||||||||

| MCLK Monitor | OPT | DIS | OFF | ||||||||||

| PMU | POR monitor | EN | |||||||||||

| BOR monitor | EN | OFF | |||||||||||

| Core regulator | FULL DRIVE | REDUCED DRIVE | LOW DRIVE | OFF | |||||||||

| Core Functions | CPU | EN | DIS | OFF | |||||||||

| DMA | OPT | DIS (triggers supported) | OFF | ||||||||||

| Flash | EN | DIS | OFF | ||||||||||

| SRAM | EN | DIS | OFF | ||||||||||

| Peripherals |

PD1 Peripherals |

OPT | DIS | OFF | |||||||||

|

PD0 Peripherals |

OPT |

OPT |

OFF | ||||||||||

| Analog | TRNG | OPT | OFF | ||||||||||

| ADC | OPT | NS (triggers supported) | OFF | ||||||||||

| 12-bit DAC | OPT | NS | OFF | ||||||||||

| OPA | OPT | NS | OPT | NS | OPT | NS | OFF | ||||||

| GPAMP | OPT | NS | OFF | ||||||||||

| COMP / 8-bit DAC | OPT | OPT (ULP only) | OPT | OPT (ULP only) | OPT | OPT (ULP only) | OFF | ||||||

| IOMUX and IO Wakeup | EN | DIS w/ WAKE | |||||||||||

| Wake Sources | N/A | ANY IRQ | PD0 IRQ | IOMUX, NRST | |||||||||