SLAAED8 October 2024 TAC5212 , TAC5412-Q1

2.3 Signal Generator 1 Frequency

Registers B0_P18_R32 (0x20) to B0_P1_R47 (0x2F) configure SG1 frequency. SG1 frequency configuration comes after amplitude and output channel configurations. Refer to Section 2.2.

This set of equations generates register coefficients for SG1 frequency configuration:

Pay attention to the right shift by 1-bit on the LSB values generated. This is important for executing correct I2C commands. These formulas generate the most significant bit (msb) and least significant bit (lsb) values that make up the I2C command script for SG1 frequency configuration.

SG1 frequency configuration is a pair of 32-bit I2C commands writing a single frequency to all output channels. No channel is isolated in this frequency configuration. Signals only appear on any output channel based on channel selection configurations. Refer to Section 2.2.

SG1 maintains the same frequency across all channels selected. Generally, one amplitude and frequency configuration is maintained across all channels for both SG1 and SG2.

Below is an example script template for SG1 frequency configuration. This script template shows register coefficients placements. This is based off results from h_msb, h_lsb, y_msb, and y_lsb equations above and the SG1 example script at the end of this section.

#Based off SG1's 600Hz example script.

#64-bit command from SG1 to OUT1

#w a0 20 [31:24] [23:16] [15:8] [7:0] [31:24] [23:16] [15:8] [7:0]

#64-bit command from SG1 to OUT2

#w a0 28 [31:24] [23:16] [15:8] [7:0] [31:24] [23:16] [15:8] [7:0]

#based off SG1 frequency equations.

#w a0 20 [h_msb] [y_msb ]

#w a0 28 [h_lsb, right shift by 1-bit] [y_lsb, right shift by 1-bit]

#600Hz from SG1.

w a0 20 99 7f ec 00 7f 9a fc b8 #[h_msb] [y_msb]

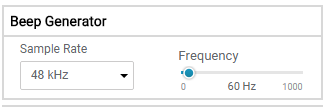

w a0 28 1c ea f1 80 0a 0a f2 99 #[h_lsb] [y_lsb] In PPC3, SG1 frequency configuration is done using the frequency scroll GUI. Figure 2-3 is an image of SG1 frequency scroll GUI.

Figure 2-3 SG1 Frequency Configuration GUI

Figure 2-3 SG1 Frequency Configuration GUI| Page | Register | Description |

|---|---|---|

0x12 | 0x20 | Programmable OUT1 BEEP GEN sin(x) coefficient byte [31:24] |

| 0x12 | 0x21 | Programmable OUT1 BEEP GEN sin(x) coefficient byte [23:16] |

| 0x12 | 0x22 | Programmable OUT1 BEEP GEN sin(x) coefficient byte [15:8] |

| 0x12 | 0x23 | Programmable OUT1 BEEP GEN sin(x) coefficient byte [7:0] |

| 0x12 | 0x24 | Programmable OUT1 BEEP GEN cos(x) coefficient byte [31:24] |

| 0x12 | 0x25 | Programmable OUT1 BEEP GEN cos(x) coefficient byte [23:16] |

| 0x12 | 0x26 | Programmable OUT1 BEEP GEN cos(x) coefficient byte [15:8] |

0x12 | 0x27 | Programmable OUT1 BEEP GEN cos(x) coefficient byte [7:0] |

| 0x12 | 0x28 | Programmable OUT2 BEEP GEN sin(x) coefficient byte [31:24] |

| 0x12 | 0x29 | Programmable OUT2 BEEP GEN sin(x) coefficient byte [23:16] |

| 0x12 | 0x2A | Programmable OUT2 BEEP GEN sin(x) coefficient byte [15:8] |

| 0x12 | 0x2B | Programmable OUT2 BEEP GEN sin(x) coefficient byte [7:0] |

| 0x12 | 0x2C | Programmable OUT2 BEEP GEN cos(x) coefficient byte [31:24] |

| 0x12 | 0x2D | Programmable OUT2 BEEP GEN cos(x) coefficient byte [23:16] |

| 0x12 | 0x2E | Programmable OUT2 BEEP GEN cos(x) coefficient byte [15:8] |

| 0x12 | 0x2F | Programmable OUT2 BEEP GEN cos(x) coefficient byte [7:0] |

# Key: w a0 XX YY ==> write to I2C address 0xa0, to register 0xXX, data 0xYY

# # ==> comment delimiter

#

#The following list gives an example sequence of items that must be #executed in the time between powering the device up and reading data #from the device. Note that there are other valid sequences depending #on which features are used.

#See the corresponding EVM user guide for jumper settings and audio #connections.

#

# Line-Out Fully-Differential 2-channel : OUT1P_M- Ch1, OUT2P_M- Ch2.

# FSYNC = 48 kHz (Output Data Sample Rate), BCLK = 12.288 MHz (BCLK/FSYNC = 256) ###################################################################

#SG1 example script

#SG1; DAC1 OUT1P & OUT1M; Differential 600Hz

w a0 00 00 # locate page x00

w a0 01 01 # device reset

w a0 02 09 # vref and dreg enable

w a0 00 01 # locate page x01

w a0 2d 08 # enable SG1

#Channel selection and amplitude configuration

w a0 00 11 # locate page 0x11

w a0 68 40 00 40 00 # mix SG1 to DAC1 L & R Channels and

# set the amplitude to full-scale, 0dB.

#Frequency configuration

w a0 00 00 # locate page 0x00

w a0 7f 00 # locate book 0x00

w a0 00 12 # locate page 0x12

#600Hz

w a0 20 99 7f ec 00 7f 9a fc b8 #sinx and cosx upper bits

w a0 28 1c ea f1 80 0a 0a f2 99 #sinx and cosx lower bits

#Output configuration

w a0 00 00 # locate page 0x00

#differential mode is the default output mode

#w a0 64 24 #option to set to single-ended mode

w a0 76 0c #enable DAC1, CH 1 & 2 180deg out of phase diff. mode

w a0 78 40 #enable DAC