SLAAED9 November 2023 TAA5412-Q1 , TAC5311-Q1 , TAC5312-Q1 , TAC5411-Q1 , TAC5412-Q1

- 1

- Abstract

- Trademarks

- 1 Introduction

- 2 Diagnostic Monitoring Architecture

- 3 Monitored Faults

- 4 Enabling Diagnostics and Programming Thresholds

- 5 Fault Diagnostic Setup Procedure

-

6 Fault Reporting

- 6.1

Live Registers

- 6.1.1 CHx_LIVE Register (page = 0x01, address = 0x3D) [Reset = 0b]

- 6.1.2 CH1_LIVE Register (page = 0x01, address = 0x3E) [Reset = 0h]

- 6.1.3 INT_LIVE0 Register (page = 0x01, address = 0x3C) [Reset = 00]

- 6.1.4 INT_LIVE1 Register (page = 0x00, address = 0x42) [reset = 0x00]

- 6.1.5 INT_LIVE2 Register (page = 0x00, address = 0x43) [reset = 0x00]

- 6.2 Latched Registers

- 6.3 Fault Filtering and Response Time

- 6.1

Live Registers

- 7 Responding to a Fault

- 8 Using PurePath Console

- 9 Diagnostic Monitoring Registers

- 10Summary

- 11References

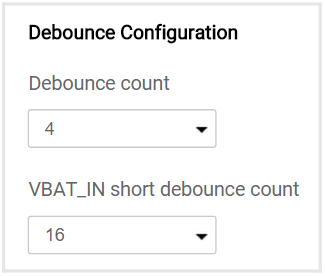

8.2.2 Debounce Configuration

Figure 8-3 shows a section of the Advanced Mode Tab that allows the user to program debounce for 0, 4, 8, or 16 counts to filter out transient events. This setting configures debounce for all faults except the VBAT_IN short, which can be programmed independently to 8 or 16 counts.

Figure 8-3 Debounce Configuration

Pane

Figure 8-3 Debounce Configuration

Pane