SLAAEJ0 November 2023 AM625 , MSPM0L1306

1.2 AM62x Processor

AM62x Processor

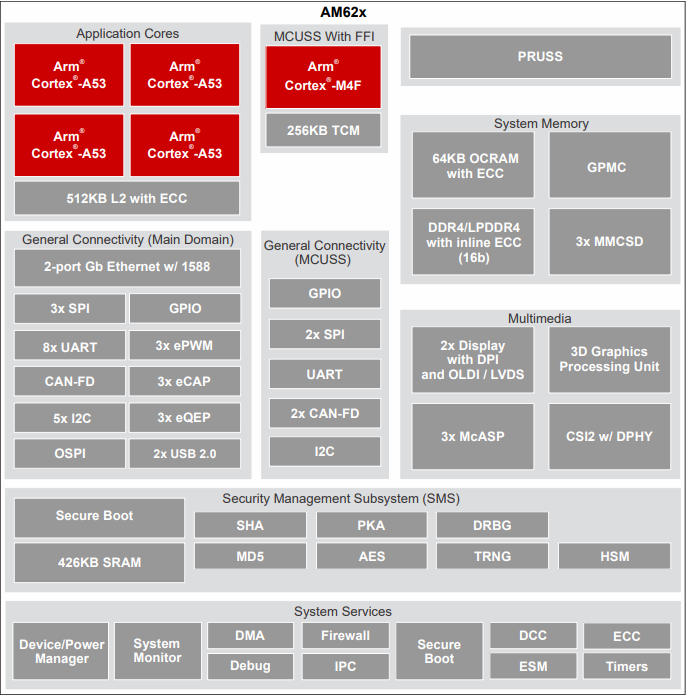

The AM62x Sitara Microprocessor, shown in Figure 1-2, is a heterogeneous processor designed for a wide variety of embedded applications. SPI can be enabled through MAIN domain on A53 Core. Figure 1-2 shows a simplified block diagram for AM62x.

For more details, see AM62x Sitara Processors Data Sheet.

Figure 1-2 AM62x Simplified Block Diagram.

Figure 1-2 AM62x Simplified Block Diagram.