-

HD3SS6126 USB 3.0 and USB 2.0 Differential Switch 2:1/1:2 MUX/DEMUX

- 1 Features

- 2 Applications

- 3 Description

- 4 Revision History

- 5 Pin Configuration and Functions

- 6 Specifications

- 7 Detailed Description

- 8 Application and Implementation

- 9 Power Supply Recommendations

- 10Layout

- 11Device and Documentation Support

- 12Mechanical, Packaging, and Orderable Information

- IMPORTANT NOTICE

HD3SS6126 USB 3.0 and USB 2.0 Differential Switch 2:1/1:2 MUX/DEMUX

1 Features

- Ideal for USB Applications

- Three Bidirectional Differential Pair Channel MUX/DEMUX Switches Also Suitable for DisplayPort, PCIe Gen1/2/3, SATA 1.5/3/6G, SAS 1.5/3/6G and XAUI Applications

- Supports Data Rates up to 10 Gbps on High-Bandwidth Path (SS)

- VCC Operating Range 3.3 V ± 10%

- Wide –3-dB Differential BW of More Than 10 GHz on High-Bandwidth Path (SS)

- Uses a Unique Adaptation Method to Maintain a Constant Channel Impedance Over the Supported Common-Mode Voltage Range

- Excellent High-bandwidth Path Dynamic Characteristics (at 2.5 GHz)

- Crosstalk = –35 dB

- Isolation = –23 dB

- Insertion Loss = –1.1 dB

- Return Loss = –11 dB

- Small 3.5 mm × 9 mm, 42-Pin WQFN Package (RUA)

- Active Mode Power = 8 mW

2 Applications

- Desktop PCs

- Notebook PCs

- Tablets

- Docking Stations

- Telecommunications

- Televisions

3 Description

The HD3SS6126 device is a high-speed, passive switch that is designed for USB applications to route both SuperSpeed USB RX and TX and USB 2.0 DP and DM signals from a source to two destinations or vice versa. The device can also be used for DisplayPort, PCI-Express™, SATA, SAS, and XAUI applications. The HD3SS6126 device can be used in either sink-side or source-side applications.

Device Information(1)

| PART NUMBER | PACKAGE | BODY SIZE (NOM) |

|---|---|---|

| HD3SS6126 | WQFN (42) | 9.00 mm × 3.50 mm |

- For all available packages, see the orderable addendum at the end of the data sheet.

Typical Application Diagram

4 Revision History

Changes from * Revision (November 2013) to A Revision

- Added Pin Configuration and Functions section, ESD Ratings table, Typical Characteristics section, Feature Description section, Device Functional Modes, Application and Implementation section, Power Supply Recommendations section, Layout section, Device and Documentation Support section, and Mechanical, Packaging, and Orderable Information section Go

5 Pin Configuration and Functions

Pin Functions

| PIN | I/O | DESCRIPTION | |

|---|---|---|---|

| NAME | NO. | ||

| GND | 10, 14, 17, 19, 21 |

Supply | Ground |

| HSA(p) | 8 | I/O | Port A USB 2.0 positive signal |

| HSA(n) | 7 | Port A USB 2.0 negative signal | |

| HSB(p) | 31 | I/O | Port B USB 2.0 positive signal |

| HSB(n) | 32 | Port B USB 2.0 negative signal | |

| HSC(p) | 33 | I/O | Port C USB 2.0 positive signal |

| HSC(n) | 34 | Port C USB 2.0 negative signal | |

| HS_OE | 6 | I (Control) | Output Enable H = Power Down L = Normal Operation |

| NC | 1, 2, 3, 4, 5, 18, 35, 36, 37, 38, 39, 40, 41, 42 |

— | Electrically No Connection |

| SEL | 9 | I (Control) | USB 3.0/2.0 Port Selection Control Pins |

| SSA0(p) | 11 | I/O | Port A, Channel 0, USB 3.0 Positive Signal |

| SSA0(n) | 12 | Port A, Channel 0, USB 3.0 Negative Signal | |

| SSA1(p) | 15 | I/O | Port A, Channel 1, USB 3.0 Positive Signal |

| SSA1(n) | 16 | Port A, Channel 1, USB 3.0 Negative Signal | |

| SSB0(p) | 29 | I/O | Port B, Channel 0, USB 3.0 Positive Signal |

| SSB0(n) | 28 | Port B, Channel 0, USB 3.0 Negative Signal | |

| SSB1(p) | 27 | I/O | Port B, Channel 1, USB 3.0 Positive Signal |

| SSB1(n) | 26 | Port B, Channel 1, USB 3.0 Negative Signal | |

| SSC0(p) | 25 | I/O | Port C, Channel 0, USB 3.0 Positive Signal |

| SSC0(n) | 24 | Port C, Channel 0, USB 3.0 Negative Signal | |

| SSC1(p) | 23 | I/O | Port C, Channel 1, USB 3.0 Positive Signal |

| SSC1(n) | 22 | Port C, Channel 1, USB 3.0 Negative Signal | |

| VDD | 13, 20, 30 | Supply | 3.3-V power supply voltage |

6 Specifications

6.1 Absolute Maximum Ratings

over operating free-air temperature range (unless otherwise noted)(1)| MIN | MAX | UNIT | ||

|---|---|---|---|---|

| Supply Voltage, VDD(2) | –0.3 | 4 | V | |

| Voltage | Differential I/O, High-bandwidth signal path: SSA0/1(p/n), SSB0/1(p/n), SSC0/1(p/n) | –0.5 | 4 | V |

| Differential I/O, Low-bandwidth signal path: HSAp/n), HSB(p/n), HSC(p/n) | -0.5 | 7 | ||

| Control pin and single ended I/O | –0.3 | VDD + 0.3 | ||

| Continuous power dissipation | See Thermal Information | |||

| Storage temperature, Tstg | –65 | 150 | °C | |

6.2 ESD Ratings

| VALUE | UNIT | |||

|---|---|---|---|---|

| V(ESD) | Electrostatic discharge | Human body model (HBM), per ANSI/ESDA/JEDEC JS-001(1) | ±2000 | V |

| Charged device model (CDM), per JEDEC specification JESD22-C101(2) | ±500 | |||

6.3 Recommended Operating Conditions

typical values for all parameters are at VCC = 3.3 V and TA = 25°C; all temperature limits are specified by design| MIN | NOM | MAX | UNIT | |||

|---|---|---|---|---|---|---|

| VDD | Supply voltage | 3.0 | 3.3 | 3.6 | V | |

| VIH | Input high voltage | Control Pins | 2.0 | VDD | V | |

| VIL | Input low voltage | Control Pins | –0.1 | 0.8 | V | |

| VI/O_Diff | Differential voltage | Switch I/O differential voltage for High-bandwidth signal path only: SSA0/1(p/n), SSB0/1(p/n), SSC0/1(p/n) | 0 | 1.8 | Vp-p | |

| VI/O_CM | Common voltage | Switch I/O common mode voltage for High-bandwidth signal path only: SSA0/1(p/n), SSB0/1(p/n), SSC0/1(p/n) | 0 | 2.0 | V | |

| TA | Operating free-air temperature | 0 | 70 | °C | ||

6.4 Thermal Information

| THERMAL METRIC | HD3SS6126 | UNIT | |

|---|---|---|---|

| RUA (WQFN) | |||

| 42 PINS | |||

| RθJA | Junction-to-ambient thermal resistance | 53.8 | °C/W |

| RθJC(top) | Junction-to-case (top) thermal resistance | 38.2 | °C/W |

| RθJB | Junction-to-board thermal resistance | 27.4 | °C/W |

| ψJT | Junction-to-top characterization parameter (1) | 5.6 | °C/W |

| ψJB | Junction-to-board characterization parameter (1) | 27.3 | °C/W |

6.5 Electrical Characteristics – Device Parameters

over recommended operating conditions (unless otherwise noted)| PARAMETER | TEST CONDITIONS | MIN | TYP | MAX | UNIT | |

|---|---|---|---|---|---|---|

| ICC | Supply current | VDD = 3.6 V, SEL = VDD /GND; OE = GND; Outputs Floating | 2.4 | 3 | mA | |

| SEL | ||||||

| IIH | Input high current | VDD = 3.6 V, VIN = VDD | 95 | µA | ||

| IIL | Input high current | VDD = 3.6 V, VIN = GND | 1 | µA | ||

| HS_OE | ||||||

| IIH | Input high current | VDD = 3.6 V, VIN = VDD | 1 | µA | ||

| IIL | Input high current | VDD = 3.6 V, VIN = GND | 1 | µA | ||

| SSA0/1, SSB0/1, SSC0/1 | ||||||

| ILK | High-impedance leakage current | VDD = 3.6 V, VIN = 2 V, VOUT= 2 V, (ILK on open outputs Port B and C) |

130 | µA | ||

| VDD = 3.6 V, VIN = 2 V, VOUT= 2 V, (ILK on open outputs Port A) |

4 | |||||

| HSA, HSB, HSC | ||||||

| ILK | High-impedance leakage current | VDD = 3.6 V, VIN = 0 V, VOUT= 0 V to 4 V, HS_OE_IN = GND |

1 | µA | ||

6.6 Electrical Characteristics – Signal Switch Parameters

under recommended operating conditions; RL, RSC = 50 Ω, CL = 10 pF (unless otherwise noted)| PARAMETER | TEST CONDITIONS | MIN | TYP | MAX | UNIT | |

|---|---|---|---|---|---|---|

| SSA0/1(p/n), SSB0/1(p/n), SSC0/1(p/n) Signal Path | ||||||

| CON | Outputs ON capacitance | VIN = 0 V, outputs open, switch ON | 1.5 | pF | ||

| COFF | Outputs OFF capacitance | VIN = 0 V, outputs open, switch OFF | 1 | pF | ||

| RON | Output ON resistance | VDD = 3.3 V, VCM = 0 V – 2 V, IO = –8 mA |

5 | 8 | Ω | |

| ΔRON | ON resistance match between pairs of the same channel | VDD = 3.3 V; 0 V ≤ VIN ≤ 2 V; IO = –8 mA |

0.7 | Ω | ||

| RFLAT_ON | ON resistance flatness (RON(MAX)– RON(MIN) |

VDD = 3.3 V; –0 V ≤ VIN ≤ 2 V | 1.15 | Ω | ||

| RL | Differential return loss (VCM = 0 V) |

f = 0.3 MHz | –25 | dB | ||

| f = 2.5 GHz | –11 | |||||

| f = 4 GHz | –11 | |||||

| XTALK | Differential crosstalk (VCM = 0 V) |

f = 0.3 MHz | -85 | dB | ||

| f = 2.5 GHz | –35 | |||||

| f = 4 GHz | –33 | |||||

| OIRR | Differential off-isolation (VCM = 0 V) |

f = 0.3 MHz | -85 | dB | ||

| f = 2.5 GHz | -23 | |||||

| f = 4 GHz | –21 | |||||

| IL | Differential insertion loss (VCM = 0 V) |

f = 0.3 MHz | –0.43 | dB | ||

| f = 2.5 GHz | –1.1 | |||||

| f = 4 GHz | –1.3 | |||||

| BW | Bandwidth | At –3 dB | 10 | GHz | ||

| HSA(p/n), HSB(p/n), HSC(p/n) SIGNAL PATH | ||||||

| CON | Outputs ON capacitance | VIN = 0 V, Outputs Open, Switch ON | 6 | 7.5 | pF | |

| COFF | Outputs OFF capacitance | VIN = 0 V, Outputs Open, Switch OFF | 3.5 | 6 | pF | |

| RON | Output ON resistance | VDD = 3 V, VIN = 0 V, IO = 30 mA |

3 | 6 | Ω | |

| VDD = 3 V, VIN = 2.4 V, IO = 30 mA |

3.4 | 6 | ||||

| ΔRON | ON resistance match between pairs of the same channel | VDD = 3 V; VIN = 0 V; IO = 30 mA |

0.2 | Ω | ||

| VDD = 3 V; VIN = 1.7 V; IO = -15 mA |

0.2 | |||||

| RFLAT_ON | ON resistance flatness (RON(MAX)– RON(MIN ) |

VDD = 3 V; VIN = 0 V; IO = 30 mA |

1 | Ω | ||

| VDD = 3 V; VIN = 1.7 V; IO = –15 mA |

1 | |||||

| XTALK | Differential crosstalk (VCM = 0 V) | RL = 50 Ω, f = 250 MHz | –40 | dB | ||

| OIRR | Differential off-isolation (VCM = 0 V) | RL = 50 Ω, f = 250 MHz | –41 | dB | ||

| BW | Bandwidth | RL = 50 Ω | 0.9 | GHz | ||

6.7 Switching Characteristics

over operating free-air temperature range (unless otherwise noted)| PARAMETER | TEST CONDITIONS | MIN | TYP | MAX | UNIT | |

|---|---|---|---|---|---|---|

| SSA0/1(p/n), SSB0/1(p/n), SSC0/1(p/n) Signal Path | ||||||

| ton | SEL-to-Switch ton | RSC and RL = 50 Ω, See Figure 1 | 70 | 250 | ns | |

| toff | SEL-to-Switch toff | RSC and RL = 50 Ω, See Figure 1 | 70 | 250 | ns | |

| tPD | Switch propagation delay | RSC and RL = 50 Ω, See Figure 3 | 85 | ps | ||

| tSK(O) | Interpair output skew (CH-CH) | RSC and RL = 50 Ω, See Figure 3 | 20 | ps | ||

| tSK(b-b) | Intrapair Output Skew (bit-bit) | RSC and RL = 50 Ω, See Figure 3 | 8 | ps | ||

| HSA(p/n), HSB(p/n), HSC(p/n) SIGNAL PATH | ||||||

| tON | SEL to Switch tON | See Figure 2 | 30 | ns | ||

| HS_OE to Switch tON | See Figure 2 | 17 | ||||

| tOFF | SEL to Switch tOFF | See Figure 2 | 12 | ns | ||

| HS_OE to Switch tOFF | See Figure 2 | 10 | ||||

| tPD(1) | Switch propagation delay | See Figure 3 | 250 | ps | ||

| tSK(O)(1) | Interpair output skew (CH-CH) | 100 | 200 | ps | ||

| tSK(P)(1) | Intrapair Output Skew (bit-bit) | 100 | 200 | ps | ||

Figure 1. Select to Switch tON and tOFF

Figure 1. Select to Switch tON and tOFF

Figure 2. Turnon (tON) and Turnoff Time (tOFF)

Figure 2. Turnon (tON) and Turnoff Time (tOFF)

Figure 3. Propagation Delay and Skew

Figure 3. Propagation Delay and Skew

6.8 Typical Characteristics

Figure 4. Intrapair Skew SSA to SSB Port

Figure 4. Intrapair Skew SSA to SSB Port

Figure 5. Intrapair Skew SSA to SSC Port

Figure 5. Intrapair Skew SSA to SSC Port

7 Detailed Description

7.1 Overview

The HD3SS6126 is a USB 3.0 and USB 2.0 differential switch, it is designed to support data rates up to 10 Gbps on high-bandwidth paths (SS), it is also suitable for DisplayPort, PCIe Gen1/2/3, SATA 1.5/3/6G, SAS 1.5/3/6G and XAUI applications. The device uses a unique adaptation method to maintain a constant channel impedance over the supported common-mode voltage range, resulting in an excellent high-bandwidth path dynamic characteristics (at 2.5 GHz; Crosstalk = –35 dB, Isolation = –23 dB, Insertion Loss = –1.1 dB, Return Loss = –11 dB).

7.2 Functional Block Diagram

7.3 Feature Description

The HD3SS6126 can be powered by VBUS from the USB Host, and is capable of selecting USB2 independently from USB3. Although the main application of the HD3SS6126 is USB3.0/2.0, the device also supports common interfaces such as PCIe Gen1 and Gen2, DP and SATA/SAS applications. The device is able to support these additional interfaces because of its support of data rates up to 5.4 Gbps and common-mode voltages from 0 V to 2 V with a maximum signal swing of 1.8 V. All of these applications use an 8b or 10b coding technique to achieve DC balance and facilitate terminal equipment.

NOTE

The device may need AC capacitors and additional bias voltage to support the PCIe Gen1 and Gen2 interfaces.

7.4 Device Functional Modes

Table 1. Truth Table USB 3.0 SuperSpeed USB

| SEL | USB 3.0 PORT SELECTION | ||

|---|---|---|---|

| SSA0/1 | SSB0/1 | SSC0/1 | |

| 0 | To/From SSB0/1 | To/From SSA0/1 | Off |

| 1 | To/From SSC0/1 | Off | To/From SSA0/1 |

Table 2. Truth Table USB 2.0 High-Speed, Full-Speed, Low-Speed Path

| HS_OE | SEL | USB 2.0 Port Selection | ||

|---|---|---|---|---|

| HSA | HSB | HSC | ||

| 0 | 0 | To/From HSB | To/From HSA | Off |

| 0 | 1 | To/From HSC | Off | To/From HSA |

| 1 | X | Off | Off | Off |

8 Application and Implementation

NOTE

Information in the following applications sections is not part of the TI component specification, and TI does not warrant its accuracy or completeness. TI’s customers are responsible for determining suitability of components for their purposes. Customers should validate and test their design implementation to confirm system functionality.

8.1 Application Information

A typical application for the HD3SS6126 is a USB 3.0 KVM switch, where one of two USB hosts system can be selected for an USB device. These guidelines are also suitable for PCIe(Gen1,Gen2), SATA, XAUI and DP, since the HD3SS6126 device is fully compatible with these protocols.

8.2 Typical Application

Figure 6. Two Signal Sources to One Destination

Figure 6. Two Signal Sources to One Destination

Figure 7. One Signal Sources to Two Destination

Figure 7. One Signal Sources to Two Destination

8.2.1 Design Requirements

Power supply requirements:

- VDD from 3 V to 3.6 V

Control pins requirements

- VIH from 2 V to VDD

- VIL from –0.1 V to 0.8 V

Differential pairs requirements:

- VI/O_Diff from 0 V to 1.8 Vp-p

- VI/O_CM from 0 V to 2 V

TA Operating free-air temperature from 0°C to 70°C

8.2.2 Detailed Design Procedure

8.2.2.1 Power Supply

The first step is to design the power supply and determine the VCC stability and minimum current required (see Power Supply Recommendations).

8.2.2.2 Differential Pairs

All of the interfaces the HD3SS6126 device supports require AC coupling between the transmitter and receiver. TI recommends using 0402-sized capacitors to provide AC coupling, but 0603-sized capacitors are also acceptable. Both 0805-sized capacitors and C-packs should be avoided. Best practice is to place AC-coupling capacitors symmetrically. A capacitor value of 0.1uF is best and the value should be matched for the +/-signal pair. The placement should be along the TX pairs on the system board, which are usually routed on the top layer of the board.

All differential pairs must have a matched impedance according to the implemented protocol: 100-Ω differential (±10%) for PCIe and 90-Ω differential (±15%) for USB 2.0 and USB 3.0.

The control logic can be implemented by use of an external control processor or by using a simple selector switch. TI recommends using 5-kΩ pullup and pulldown resistors on the control signals, if they are included. The control logic must not violate the input voltage parameters outlined in the Recommended Operating Conditions table.

8.2.3 Application Curves

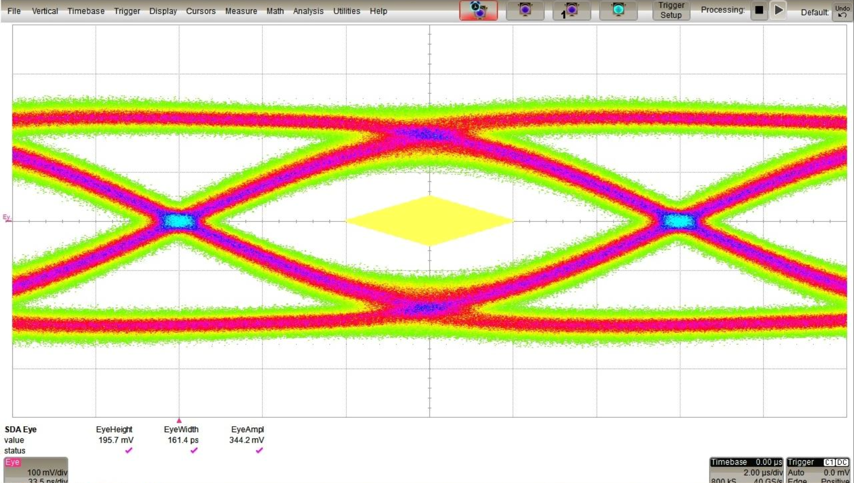

Figure 8. USB 3.0 TX Eye Pattern Test With 3-Inch 5-mil Differential PCB Trace Without HD3SS6126

Figure 8. USB 3.0 TX Eye Pattern Test With 3-Inch 5-mil Differential PCB Trace Without HD3SS6126

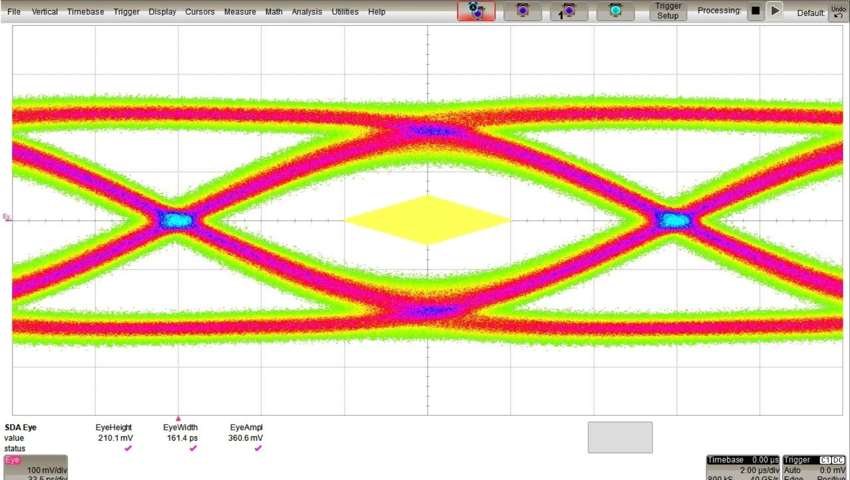

Figure 9. USB 3.0 TX Eye Pattern Test With 3-Inch 5-mil Differential PCB Trace With HD3SS6126

Figure 9. USB 3.0 TX Eye Pattern Test With 3-Inch 5-mil Differential PCB Trace With HD3SS6126

9 Power Supply Recommendations

The power supply must provide a constant voltage with a 10% maximum variation of the nominal value, and has to be able to provide at least 3 mA for the HD3SS6126 only (based on the maximum power consumption). It is also possible to provide the power supply from VBUS from the Host, just by including a voltage regulator powered through VBUS. Each VCC pin must have a 0.1-µF bypass capacitor placed as closely as possible. TI recommends including two extra capacitors in parallel, which should be also placed as closely as possible to the VCC pin. The suggested values for these extra capacitors are 1 µF and 0.01 µF.