SLAU892A March 2023 – June 2024 AFE11612-SEP

3.2.2.1.1 DACs Subpage

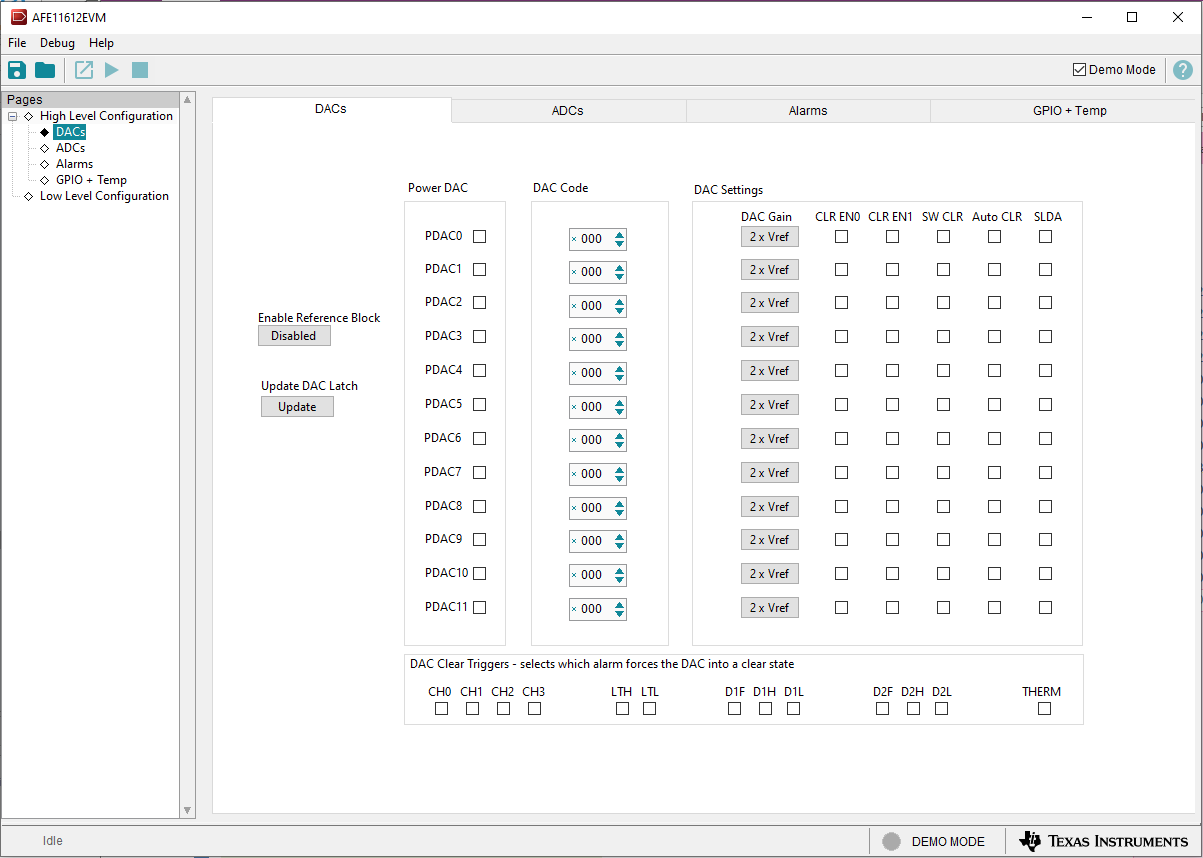

Figure 4-6 shows the DACs subpage. The DAC page gives the user an interface to observe and control the different data registers, modes, and configurations available for each individual DAC channel. The AFE11612-SEP contains 12 DACs with 12 bits of resolution. The DACs can be used with an internal or external reference. To enable each DAC channel, select the respective checkbox in the Power DAC column.

Figure 3-6 DACs Subpage

Figure 3-6 DACs Subpage