SLLSER8J June 2017 – August 2024

PRODUCTION DATA

- 1

- 1 Features

- 2 Applications

- 3 Description

- 4 Device Comparison Table

- 5 Pin Configuration and Function

-

6 Specifications

- 6.1 Absolute Maximum Ratings

- 6.2 ESD Ratings

- 6.3 Recommended Operating Conditions

- 6.4 Thermal Information

- 6.5 Power Ratings

- 6.6 Insulation Specifications for D Package

- 6.7 Insulation Specifications for DWV Package

- 6.8 Safety-Related Certifications For D Package

- 6.9 Safety-Related Certifications For DWV Package

- 6.10 Safety Limiting Values

- 6.11 Electrical Characteristics

- 6.12 Switching Characteristics

- 6.13 Insulation Characteristics Curves

- 6.14 Typical Characteristics

- 7 Parameter Measurement Information

- 8 Detailed Description

- 9 Application and Implementation

- 10Power Supply Recommendations

- 11Layout

- 12Device and Documentation Support

- 13Revision History

- 14Mechanical, Packaging, and Orderable Information

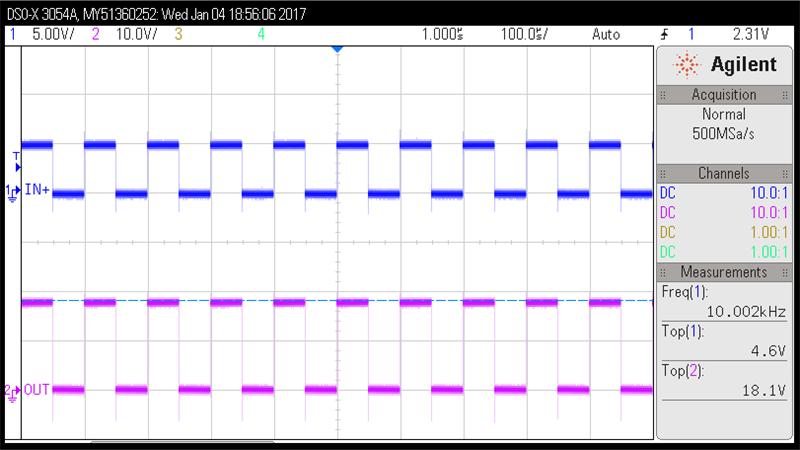

9.2.4 Application Curve

| VCC2 = 20 V | VEE2 = GND | fSW = 10 kHz |