-

Selection Considerations for Output Capacitors of Multiphase Voltage Regulators Part 1

- Selection Considerations for Output Capacitors of Multiphase Voltage Regulators Part 1

- IMPORTANT NOTICE

Selection Considerations for Output Capacitors of Multiphase Voltage Regulators Part 1

Selection Considerations for Output Capacitors of Multiphase Voltage Regulators Part 1

This application note describes the selection considerations of output capacitors, based on load transient and output impedance of processors power rails. Presently, there are no specific tools available for non-Intel processor output capacitors selection in multiphase designs. In Part 1, the minimum required output capacitance to meet low repetitive rate load transient specifications is discussed. Part 2 will describe capacitor types and value to meet output impendence requirements, and also high rate repetitive load transient specifications. Analytical and experimental results show that output capacitors selection is optimized for load transient and output impedance, to fulfill non-Intel processor requirements.

Trademarks

D-CAP+ is a registered trademark of Texas Instruments.

1 Introduction

High-performance microprocessors require low voltage and high current voltage regulator modules(VRM). The large supply current not only poses a stringent challenge on efficiency, but also heavily burdens the transient response. To ensure fast load transient, output capacitors and output impedance should be optimized.

In multiphase voltage regulators based on interleaved buck topology, the inductor selection of L is decided by current ripple, reflecting trade-off between inductor volume and power losses. Then, the output capacitance Co is based on both steady-state ripple and load transient specification(undershoot vud and overshoot vov). In most of the cases, not steady-state ripple but load transient of output voltage is the major limiting factor for output capacitance selection.

For a buck converter, some equations were provided to calculate output capacitance based on load transient, but they are under perfectly ideal cases, without taking specific load step characteristics, loop response influence, controller limitations and multiphase features into consideration. Actually, shown in Figure 2, load step characteristics like slew rate k, amplitude A, and repetitive rate (or called frequency) will highly decide how the controller responses to the load transient.

Figure 1. Multiphase Voltage Regulator Diagram

Figure 1. Multiphase Voltage Regulator Diagram  Figure 2. Undershoot and Overshoot of Load Transient

Figure 2. Undershoot and Overshoot of Load Transient When closed loop adjusts automatically, it may go into saturation as equivalent duty cycle goes to zero or maximum, with load disturbance.

Whether saturated or not, the control loop will have a key impact on load transient performance. With analysis of frequency domain bode plot, as well as system type and bandwidth, load transient with unsaturated loop can be completely described by a linear system transfer function. While the control loop is saturated, load transient should be taken over by physics, including controller limitations, and parameters like inductance and capacitance.

To clearly research on how TI controller with D-CAP+™ control would respond in non-Intel application, analysis will be done by assuming DC load-line(DCLL)=0, and dynamic phase shedding(DPS) and non-linear features(like OSR) disabled. USR feature is automatically inactive when DPS is disabled.

2 Current Transfer Function Gii_CL(s) of Load Current to Inductor Current

From Figure 1, the summation of all inductor current is called Isum, undershoot and overshoot occur when Isum cannot track Io quickly. To calculate undershoot and overshoot without DCLL, based on unbalanced electric discharges and charges of output capacitors, the relationship of Isum and Io needs to be clarified. Thus, it's important to know how inductor current IL(Isum in multiphase application) responds when load current Io varies rapidly.

Based on small-signal model of a multiphase buck converter, and the D-CAP+ control modeling, we can derive small-signal transfer functions both in open loop and closed loop, of any input to any output within the system, shown in Figure 3.

All open-loop small-signal transfer functions based on D-CAP+ control mode are listed below:

Table 1. Open-loop Small-signal Transfer Functions in D-CAP+ Control Mode

| Transfer Functions | Explanations |

|---|---|

| Gii_OP(s) | From input Io to output IL/Isum |

| Zo_OP(s) | From input Io to output vout |

| Gvi_OP(s) | From input vin to output IL/Isum |

| Gvv_OP(s) | From input vin to output vout |

| Gc2iL(s) | From input vc to output IL/Isum |

| Gc2vo(s) | From input vc to output vout |

| Hcomp(s) | Loop compensation |

For example, from input Io to output vout, the transfer function is named Zo_OP(s), representing how Io variation affects vout in open loop, also called open-loop output impendence from physical meaning.

Inside the dot line at bottom below, is the common closed-loop control loop called loop gain L(s)=Hcomp(s)*Gc2vo(s). All closed-loop transfer functions can be calculated based on open-loop transfer functions and loop gain together, with signal-flow diagram transformation in Figure 3.

Figure 3. Signal-Flow Diagram of Small-Signal Model of D-CAP+ Control

Figure 3. Signal-Flow Diagram of Small-Signal Model of D-CAP+ Control Load current Io to inductor current IL (Isum in multiphase application), as current transfer functions, are our interests here. For clarity, we define symbols as below:

- Gii_OP(s) is open-loop transfer function of Io to Isum

- Gii_CL(s) is closed-loop transfer function of Io to Isum

They describe how Io will affect Isum with specific expression, under open-loop and D-CAP+ closed-loop control in frequency domain.

Taking parameters in Table 5 as an example, the bode plot of loop gin L(s) is shown in Figure 4 with results of both simulation and bench test. We can find these two match well with cross frequency fc=~100kHz.

Figure 4. Bode Plot of Loop Gain L(s) in Simulation and Bench Test

Figure 4. Bode Plot of Loop Gain L(s) in Simulation and Bench Test The good matching result can direct us to extend the usage of simulation tool to estimate other transfer functions. By performing signal-flow diagram transformation in Figure 3, we get the closed-loop equation of Gii_CL(s):

In Figure 5, simulation shows what Gii_CL(s) looks like, when compared with Gii_OP(s) and L(s) together.

Figure 5. Bode Plot of Gii_CL(s), Gii_OP(s) and L(s) in Simulation

Figure 5. Bode Plot of Gii_CL(s), Gii_OP(s) and L(s) in Simulation In conclusion, by D-CAP+ closed-loop control, we can strongly increase the bandwidth of the Gii_OP(s) to much higher, and improve dynamic response of Isum, ensuring itself to follow Io load step as quick as possible. From Figure 5, we can approximately take Gii_CL(s) as a first-order system with corner frequency fci=1.5fc=~150kHz.

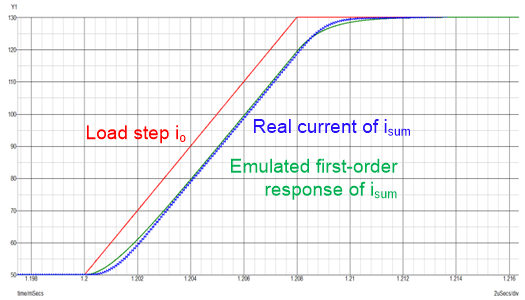

Figure 6 is one simulated example showing that real response of Isum, matches very well with emulated response of the approximate first-order system, under a given ramp-step input.

Figure 6. Response of Approximate First-Order System

Figure 6. Response of Approximate First-Order System We will use the response of this approximate Gii_CL(s) to emulate real response of Isum, under a given ramp-step load step, in a linear system without saturation.