-

TPS62933 Thermal Performance with SOT583 Package

TPS62933 Thermal Performance with SOT583 Package

Trademarks

All trademarks are the property of their respective owners.

1 Introduction

Small outline transistor (SOT) packages are widely used due to their low cost and low profile, the SOT23 is one of the most widely used SOT packages. But today more DC/DCs are using the SOT5x3 packages, whose size is even smaller than that of the SOT23 package. Due to the limit size, bonding wire technology is not recommended to use in SOT5x3 package and thus it does not have a thermal PAD. As a result, improving the thermal performance for chips with SOT5x3 package both in the IC design phase and the PCB layout design phase is necessary.

Bonding wire and FCOL have different ways to connect the die with the package. This paper shows the differences between two bump methods, and introduces a general rule for SOT5x3 package layout and gives an example of TI suggested layout. Finally, based on the layout analysis, this paper compares the thermal performance of FCOL SOT5x3 package with FCOL SOT23 package and bonding wore SO Power PAD package.

2 Bonding Wire Package Introduction

There are 500 to 1,200 chips, which are also called dies, being attached to each sheet of wafers that have completed the front-end process. A dicing process will divide the chips into individual and use wires to connect the chip with the outside so that each chip can be used for the required field. Bonding wire is a method of bonding thin metal wires to a pad, as a technology that connects the internal die and the outside.

As shown in Figure 2-1, the chip fastens on the middle of the lead frame with glue. Wires act as a bridge between the bonding pad of the chip (first bond) and the pad of the carrier (second bond). The material of the wire is copper or gold, the length is from several hundred μm to several mm and the diameter is typically 15 to 35 μm. The total RDSon is the RDSon of the die plus the bonding wire’s resistor. For a high-current converter, the resistor of the bonding wire significantly increases the total RDSon of the device, meaning to keep the total RDSon smaller, you must increase the die size to decrease the die RDSon. The bonding wire will also increase the parasitic inductance between Vin, SW pin to Vin, and the SW pad on the die. It will decrease the SW ringing slew rate because of higher parasitic inductance, which is bad for efficiency.

Figure 2-1 Simplified Structure of Bonding

Wire Package.

Figure 2-1 Simplified Structure of Bonding

Wire Package.To improve the thermal performance, the Power PAD can be added so that the leadframe die pad (or thermal pad) is exposed on the bottom of the IC. This provides an extremely low thermal resistance path between the die and the exterior of the package. The thermal pad on the bottom of the IC can then be soldered directly to the printed circuit board (PCB), using the PCB as a heatsink. In addition, through the use of thermal vias, the thermal pad can be directly connected to a ground plane or special heat sink structure designed into the PCB.

3 Flip Ship on Lead Package Introduction

Flip chip assembly is the direct electrical connection of face-down (hence, flipped) electronic components onto substrates, circuit boards, or other components, by means of conductive bumps on the chip bond pads. While in contrast, bonding wire uses face-up chips with an individual wire connected to each bond pad. Figure 3-1 is a conceptual view of a flip chip and substrate.

Figure 3-1 Simplified Structure of Flip

Chip on Lead Package

Figure 3-1 Simplified Structure of Flip

Chip on Lead PackageThe continuing boom in flip chip packaging results from flip chip’s advantages in size, performance, flexibility, reliability, and cost over other microelectronic assembly methods:

- Smallest Size – Eliminating bond wires and cumbersome individual packages reduces the required board area per chip by up to 95% and the height by more than 50%. Weight can be less than 5% of the packaged device weight. Flip chip is the simplest minimal package, smallest because it is very close to chip size.

- Highest Performance – Because of its small size, flip chip offers the highest speed electrical performance of any assembly method. Eliminating bond wires reduces the delaying inductance and capacitance of the connection by a factor of 10, and shortens the signal path by a factor of 25 to 100. The result is high speed off-chip interconnection.

- Greatest Connection Flexibility – Flip chip gives the greatest input/output connection flexibility. Wire bond connections are limited to the perimeter of the die, driving die sizes up as the number of connections increases. Flip chip connections can use the whole area of the die, accommodating many more connections on a smaller die, and placing them most efficiently. Area connections also allow 3-D stacking of die and other components.

- Most Rugged – Flip chip is mechanically the most rugged interconnection method. Flip chips, when completed with an adhesive underfill, are solid little blocks of cured epoxy. They have survived laboratory tests simulating the forces of rocket liftoff and of artillery firing, as well as millions of cumulative total hours of actual use in computers and under automobile hoods.

- Lowest Cost – Flip chip can be the lowest cost interconnection for high volume automated production, with costs of a fraction of a cent per connection. This explains flip chip’s longevity in the cost-conscious automotive world, and growing popularity in smart cards, RFID cards, cellular telephones, and other cost-dominated applications.

4 SOT 583 Package Layout Guideline

TPS62933 uses FCOL SOT583 package whose size is 1.6mm×2.1mm. It is rather small and doesn’t have a thermal pad. In order to improve the thermal performance, on time resistor of the FET is designed to have a small value, so that the power loss of the chip can be reduced. Also, PCB design should be optimized to achieve good thermal dissipation.

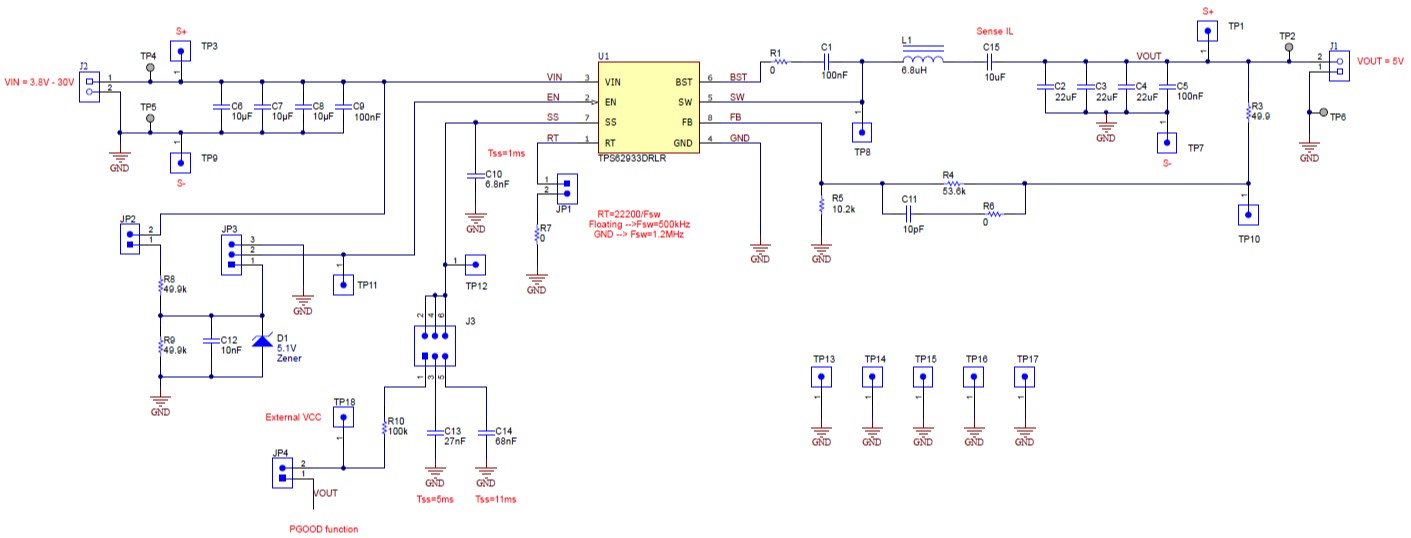

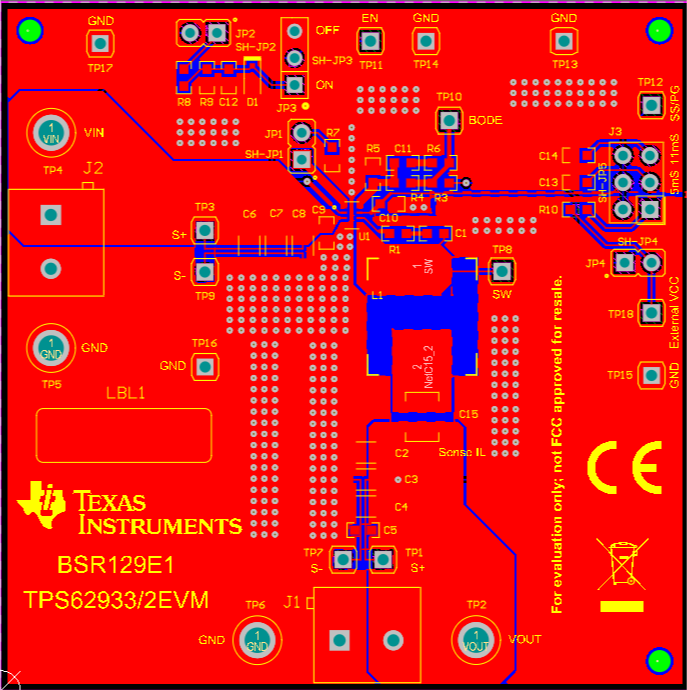

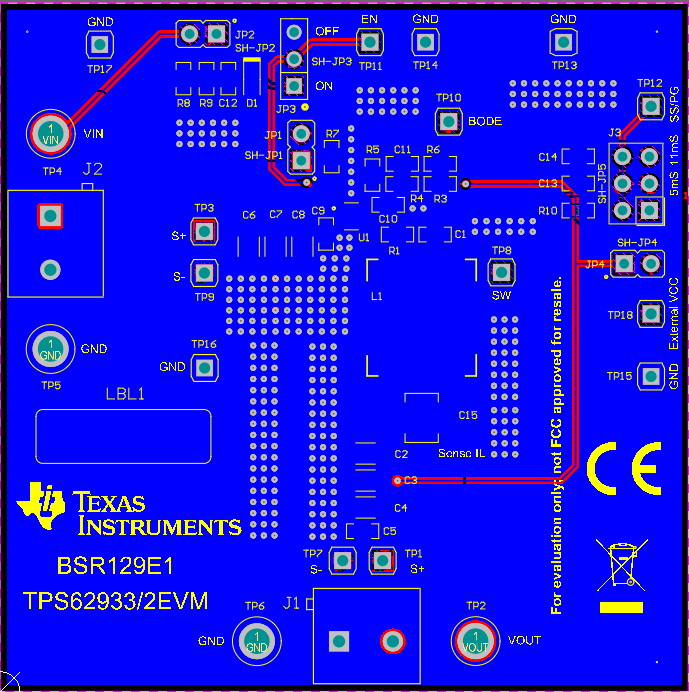

A 4-layer PCB is helpful for thermal dispassion, TI’s SOT583 solution can support a 2-layer application, TI's EVMs use a 2-layer PCB. The typical application circuit of the TPS62933 device is shown in Figure 4-1 and a layout image is provided in Figure 4-2 and Figure 4-3.

Figure 4-1 Typical Application Circuit of

TPS62933 Device

Figure 4-1 Typical Application Circuit of

TPS62933 Device Figure 4-2 Top Layer of TPS62933 EVM

Figure 4-2 Top Layer of TPS62933 EVM Figure 4-3 Bottom Layer of TPS62933 EVM

Figure 4-3 Bottom Layer of TPS62933 EVMThe layout in Figure 4-2 and Figure 4-3 is for reference. In some PCB designs, the top and bottom layer may not have so much space. In those cases, IC pins can be connected with vias to copper planes in the inner layers. It is important to realize that in FCOL packages, all IC pins are potential heat conductors and good a thermal connection to PCB copper planes can enhance the thermal cooling effect.

The following list, provides the layout priority:

- VIN and GND traces should be as wide as possible to reduce trace impedance. The wide areas provide better heat dissipation.

- The input capacitor and output capacitor should be placed as close to the device as possible to minimize trace impedance.

- Provide sufficient vias for the input capacitor and output capacitor.

- Keep the SW trace as physically short and wide as practical to minimize radiated emissions.

- Do not allow switching current to flow under the device.

- A separate VOUT path should be connected to the upper feedback resistor.

- Make a Kelvin connection to the GND pin for the feedback path.

- The voltage feedback loop should be placed away from the high-voltage switching trace, and would preferably have a ground shield.

- The trace of the VFB node should be as small as possible to avoid noise coupling.

- The GND trace between the output capacitor and the GND pin should be as wide as possible to minimize its trace impedance.

For a 4-layer PCB, put your signal wire at layer 2 or layer 3, make sure the bottom layer GND does not separate by the line, this will increase thermal dissipation. Also, add more GND via to make all GND in each layer connect together. TI suggests pouring GND polygon for the top layer and the bottom layer.