SLUSAP5A December 2011 – November 2016 TPS53316

PRODUCTION DATA.

- 1 Features

- 2 Applications

- 3 Description

- 4 Revision History

- 5 Pin Configuration and Functions

- 6 Specifications

- 7 Detailed Description

- 8 Application and Implementation

- 9 Power Supply Recommendations

- 10Layout

- 11Device and Documentation Support

- 12Mechanical, Packaging, and Orderable Information

6 Specifications

6.1 Absolute Maximum Ratings

over operating free-air temperature range (unless otherwise noted)(1)| MIN | MAX | UNIT | |||

|---|---|---|---|---|---|

| Input voltage | VIN | –0.3 | 7 | V | |

| VBST | –0.3 | 17 | |||

| VBST (with respect to LL) | –0.3 | 7 | |||

| EN | –0.3 | 7 | |||

| FB, PS, RF/OC | –0.3 | 3.7 | |||

| Output voltage | SW | DC | –1 | 7 | V |

| Pulse < 20 ns, E = 5 µJ | ≥–5 | <10 | |||

| PGD | –0.3 | 7 | |||

| COMP, VREG3 | –0.3 | 3.7 | |||

| PGND | –0.3 | 0.3 | |||

| Junction temperature, TJ | –40 | 150 | °C | ||

| Operating open-air temperature, TA | –40 | 85 | °C | ||

| Storage temperature, Tstg | –55 | 150 | °C | ||

(1) Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. These are stress ratings only, which do not imply functional operation of the device at these or any other conditions beyond those indicated under Recommended Operating Conditions. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

6.2 ESD Ratings

| VALUE | UNIT | |||

|---|---|---|---|---|

| V(ESD) | Electrostatic discharge | Human-body model (HBM), per ANSI/ESDA/JEDEC JS-001(1) | ±2000 | V |

| Charged-device model (CDM), per JEDEC specification JESD22-C101(2) | ±500 | |||

(1) JEDEC document JEP155 states that 500-V HBM allows safe manufacturing with a standard ESD control process.

(2) JEDEC document JEP157 states that 250-V CDM allows safe manufacturing with a standard ESD control process.

6.3 Recommended Operating Conditions

| MIN | MAX | UNIT | |||

|---|---|---|---|---|---|

| Input voltage | VIN (main supply) | 2.9 | 6 | V | |

| VBST | –0.1 | 13.5 | |||

| VBST (with respect to SW) | –0.1 | 6 | |||

| EN, | –0.1 | 6 | |||

| FB, PS, RF/OC | –0.1 | 3.5 | |||

| Output voltage | SW | –1 | 6.5 | V | |

| PGD | –0.1 | 6 | |||

| COMP, VREG3 | –0.1 | 3.5 | |||

| PGND | –0.1 | 0.1 | |||

| TJ | Junction temperature | –40 | 125 | °C | |

6.4 Thermal Information

| THERMAL METRIC(1) | TPS53316 | UNIT | |

|---|---|---|---|

| RGT (QFN) | |||

| 16 PINS | |||

| RθJA | Junction-to-ambient thermal resistance | 45.9 | °C/W |

| RθJC(top) | Junction-to-case (top) thermal resistance | 54.3 | °C/W |

| RθJB | Junction-to-board thermal resistance | 18.3 | °C/W |

| ψJT | Junction-to-top characterization parameter | 1.1 | °C/W |

| ψJB | Junction-to-board characterization parameter | 18.3 | °C/W |

| RθJC(bot) | Junction-to-case (bottom) thermal resistance | 5.3 | °C/W |

(1) For more information about traditional and new thermal metrics, see the Semiconductor and IC Package Thermal Metrics application report.

6.5 Electrical Characteristics

over operating free-air temperature range, VIN = 3.3 V, PGND = GND (unless otherwise noted)| PARAMETER | TEST CONDITIONS | MIN | TYP | MAX | UNIT | |

|---|---|---|---|---|---|---|

| SUPPLY: VOLTAGE, CURRENTS, AND UVLO | ||||||

| VVIN | VIN supply voltage | Nominal input voltage range | 2.9 | 6 | V | |

| IVIN(sdn) | VIN shutdown current | EN = LO | 15 | µA | ||

| IVIN | VIN supply current | EN = HI, VFB = 0.63 V, No load | 2 | 3.5 | mA | |

| VUVLO | VIN UVLO threshold | Ramp up, EN = HI | 2.8 | V | ||

| VUVLO(hys) | VIN UVLO hysteresis | VIN UVLO hysteresis | 120 | mV | ||

| VREG3 | LDO output | VVIN = 5 V, 0 ≤ IDD ≤ 5 mA | 3.135 | 3.3 | 3.465 | V |

| VOLTAGE FEEDBACK LOOP: VREF AND ERROR AMPLIFIER | ||||||

| VVREF | VREF | Internal precision reference voltage | 0.6 | V | ||

| TOLVREF | VREF tolerance | 0°C ≤ TA≤ 85°C | –1% | 1% | ||

| –40°C ≤ TA≤ 85°C | –1.25% | 1.25% | ||||

| UGBW(1) | Unity gain bandwidth | 14 | MHz | |||

| AOL(1) | Open-loop gain | 80 | dB | |||

| IFBINT | FB input leakage current | Sourced from FB pin | 30 | nA | ||

| IEA(max)(1) | Output sinking and sourcing current | CCOMP = 20 pF | 5 | mA | ||

| SR(1) | Slew rate | 5 | V/µs | |||

| OCP: OVERCURRENT AND ZERO CROSSING | ||||||

| IOCPL3A(4) | Overcurrent limit on high-side FET | 4.5-A setting, when IOUT exceeds this threshold for 4 consecutive cycles, VVIN = 3.3 V, VOUT = 1.5 V with 1-µH inductor, fSW = 1.1 MHz, TA= 25°C |

4.05 | 4.5 | 4.95 | A |

| IOCPH3A(4) | One-time overcurrent latch off on the low-side FET | 4.5-A setting, immediate shuts down when sensed current reach this value VVIN = 3.3 V, VOUT = 0.6 V with 1-µH inductor, fSW = 1.1 MHz, TA= 25°C |

4.49 | 5.1 | 5.61 | A |

| IOCPL5A(4) | Overcurrent limit on high-side FET | 6.5-A setting, when IOUT exceeds this threshold for 4 consecutive cycles, VVIN = 3.3 V, VOUT = 1.5 V with 1-µH inductor, fSW = 1.1 MHz, TA= 25°C |

6.1 | 6.8 | 7.5 | A |

| IOCPH5A(4) | One time overcurrent latch off on the low-side FET | 6.5-A setting, immediate shut down when sensed current reaches this value VVIN = 3.3 V, VOUT = 0.6 V with 1-µH inductor, fSW = 1.1 MHz, TA= 25°C |

6.75 | 7.5 | 8.3 | A |

| thiccup | Hiccup time interval | fSW = 1.1 MHz | 14.5 | ms | ||

| VZXOFF(1) | Zero crossing comparator internal offset | PGND – SW, SKIP mode | –4.5 | –3 | –1.5 | mV |

| PROTECTION: OVP, UVP, PGD, AND INTERNAL THERMAL SHUTDOWN | ||||||

| VOVP | Overvoltage protection threshold voltage | Measured at the FB w/r/t VREF | 114% | 117% | 120% | |

| VUVP | Undervoltage protection Threshold voltage | Measured at the FB w/r/t VREF | 80% | 83% | 86% | |

| VPGDL | PGD low threshold | Measured at the FB w/r/t VREF | 80% | 83% | 86% | |

| VPGDU | PGD upper threshold | Measured at the FB w/r/t VREF | 114% | 117% | 120% | |

| VINMINPG | Minimum input voltage for valid PGD at start-up | Measured at VIN with 1-mA sink current on PGD pin at start-up | 1 | V | ||

| THSD(1) | Thermal shutdown | 130 | 140 | 150 | °C | |

| THSDHYS(1) | Thermal shutdown hysteresis | Controller start again after temperature has dropped | 40 | °C | ||

| LOGIC PINS: I/O VOLTAGE AND CURRENT | ||||||

| VPGPD | PGD pull-down voltage | Pulldown voltage with 4-mA sink current | 0.1 | 0.3 | V | |

| IPGLK | PGD leakage current | Hi-Z leakage current, Apply 3.3 V in off state | –2 | 0 | 2 | µA |

| RENPU | Enable pullup resistor | 2.25 | MΩ | |||

| VENH | EN logic high | VVIN = 3.3 V | 0.82 | 0.97 | 1.1 | V |

| VVIN = 5 V | 0.95 | 1.1 | 1.25 | V | ||

| VENHYS | EN hysteresis | VVIN = 3.3 V | 0.16 | 0.24 | V | |

| VVIN = 5 V | 0.2 | 0.275 | V | |||

| PSTHS | PS mode threshold voltage | Level 1 to level 2(2) | 0.12 | V | ||

| Level 2 to level 3 | 0.4 | |||||

| Level 3 to level 4 | 0.8 | |||||

| Level 4 to level 5 | 1.4 | |||||

| Level 5 to level 6 | 2.2 | |||||

| IPS | PS source | 10-µA pull-up current when enabled | 8 | 10 | 12 | µA |

| RF/OCTHS | RF/OC pin threshold voltage | Level 1 to level 2(3) | 0.12 | V | ||

| Level 2 to level 3 | 0.4 | |||||

| Level 3 to level 4 | 0.8 | |||||

| Level 4 to level 5 | 1.4 | |||||

| Level 5 to level 6 | 2.2 | |||||

| IRF/OC | RF/OC source current | 10-µA pullup current when enabled | 8 | 10 | 12 | µA |

| BOOT STRAP: VOLTAGE AND LEAKAGE CURRENT | ||||||

| IVBSTLK | VBST leakage current | VVIN = 3.3 V, VVBST = 6.6 V, TA = 25°C | 1 | µA | ||

| TIMERS: SS, FREQUENCY, RAMP, ON-TIME AND I/O TIMING | ||||||

| tSS_1 | Delay after EN Asserting | EN = ‘HI’ | 0.2 | ms | ||

| tSS_2 | Soft-start ramp_up time | 0 V ≤ VSS ≤ 0.6 V | 0.4 | ms | ||

| 0 V ≤ VSS ≤ 0.6 V, 4 x SS time (option2) | 1.6 | |||||

| tPGDENDLY | PGD start-up delay time | VSS = 0.6 V to PGD (SSOK) going high | 0.3 | ms | ||

| VSS = 0.6 V to PGD (SSOK), option 2 | 1.2 | |||||

| tOVPDLY | OVP delay time | Time from FB out of +20% of VREF to OVP fault | 1 | 1.7 | 2.5 | µs |

| tUVPDLY | UVP delay time | Time from FB out of –20% of VREF to UVP fault | 10 | µs | ||

| fSW | Switching frequency | All modes, fSET = 0.75 MHz | 0.653 | 0.725 | 0.798 | MHz |

| All modes, fSET = 1.1 MHz | 0.99 | 1.1 | 1.21 | |||

| FCCM and DE mode, fSET = 2 MHz | 1.71 | 1.9 | 2.09 | |||

| HEF mode, fSET = 2 MHz | 1.566 | 1.8 | 2.034 | MHz | ||

| Ramp amplitude(1) | 2.9 V ≤ VVIN ≤ 6 V | VVIN/4 | V | |||

| tMIN(off) | Minimum OFF time, FCCM and DE | All frequencies | 90 | 130 | ns | |

| Minimum OFF time, HEF | fSW = 1.1 MHz | 160 | 240 | ns | ||

| DMAX | Maximum duty cycle, FCCM and DE | fSW = 1.1 MHz | 84% | 89% | ||

| DMAX | Maximum duty cycle, HEF | All frequencies | 75% | 81% | ||

| RSFTSTP | Soft-discharge transistor resistance | EN = LO, VVIN = 3.3 V, VOUT = 0.5 V | 60 | Ω | ||

(1) Ensured by design. Not production tested.

(2) See PS pin description for levels.

(3) See RF/OC pin description for levels.

6.6 Typical Characteristics

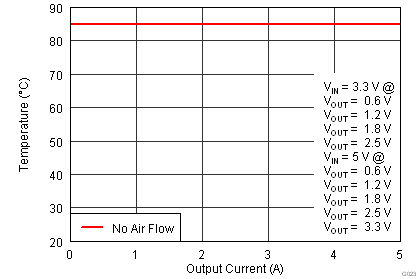

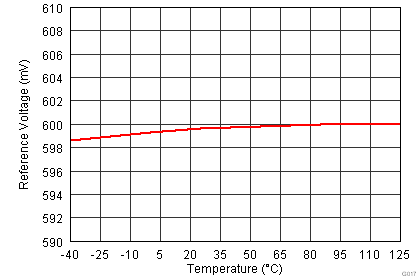

Inductor used: PCMC065T-1R0, 1 µH, 5.6 mΩ Figure 1. Reference Voltage vs Temperature

Figure 1. Reference Voltage vs Temperature

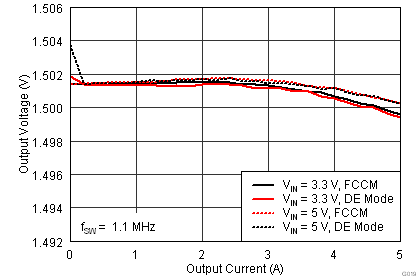

Figure 3. Output Voltage vs Output Current

Figure 3. Output Voltage vs Output Current

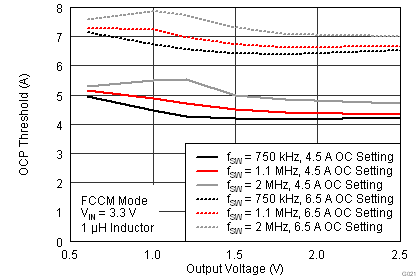

Figure 5. OCP Threshold vs Output Voltage

Figure 5. OCP Threshold vs Output Voltage

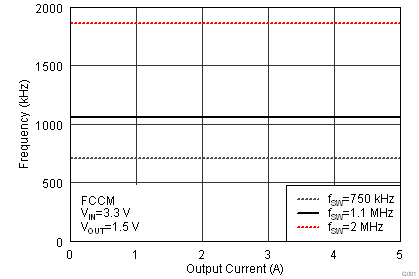

Figure 7. Frequency vs Output Current, FCCM

Figure 7. Frequency vs Output Current, FCCM

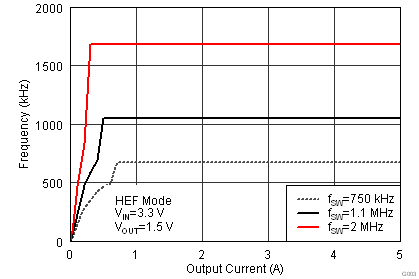

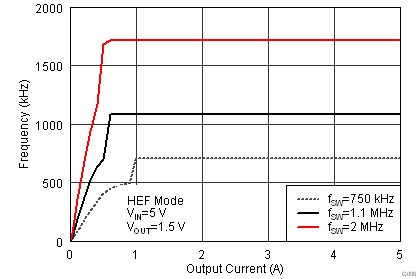

Figure 9. Frequency vs Output Current, HEF Mode

Figure 9. Frequency vs Output Current, HEF Mode

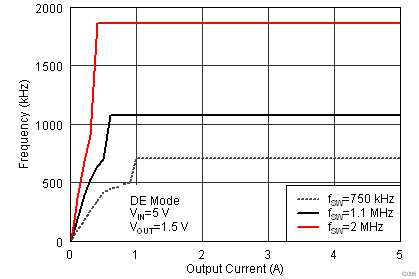

Figure 11. Frequency vs Output Current, DE Mode

Figure 11. Frequency vs Output Current, DE Mode

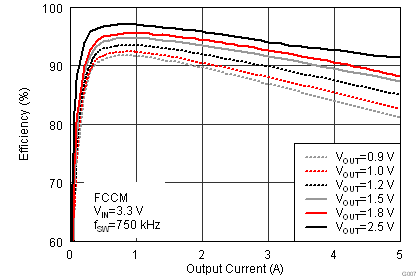

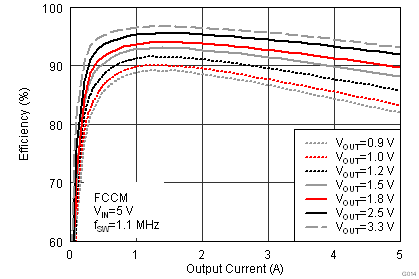

Figure 13. Efficiency vs Output Current, FCCM

Figure 13. Efficiency vs Output Current, FCCM

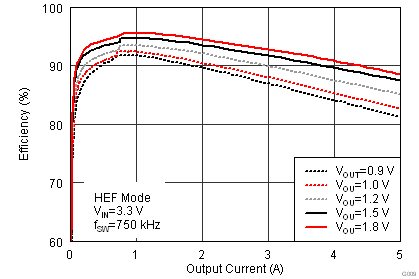

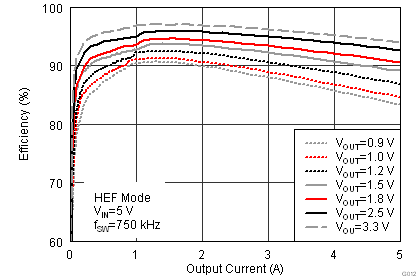

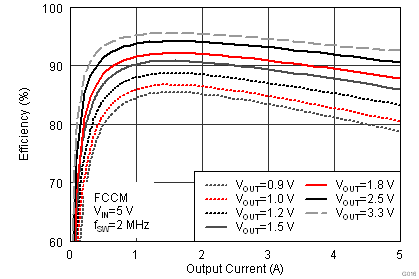

Figure 15. Efficiency vs Output Current, HEF Mode

Figure 15. Efficiency vs Output Current, HEF Mode

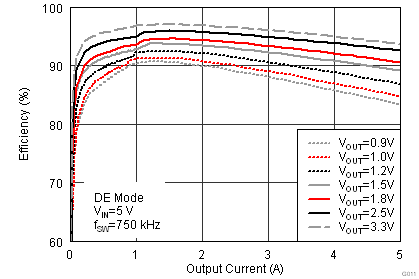

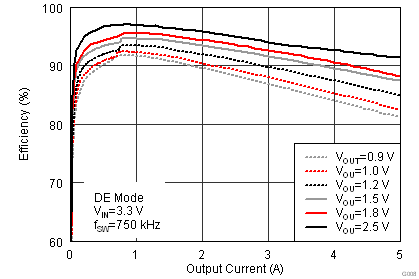

Figure 17. Efficiency vs Output Current, DE Mode

Figure 17. Efficiency vs Output Current, DE Mode

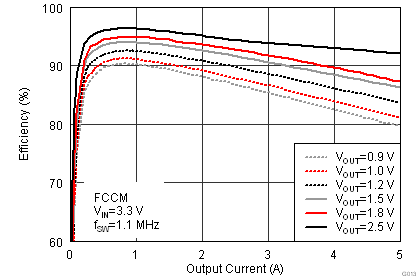

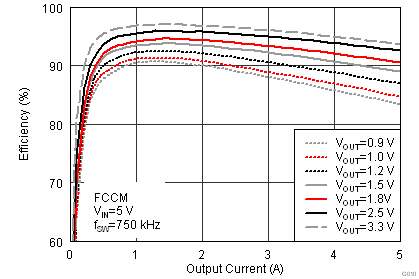

Figure 19. Efficiency vs Output Current, FCCM

Figure 19. Efficiency vs Output Current, FCCM

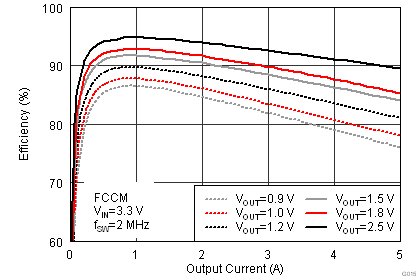

Figure 21. Efficiency vs Output Current, FCCM

Figure 21. Efficiency vs Output Current, FCCM

Figure 23. Normal Start-up

Figure 23. Normal Start-up

Figure 25. Turnoff Enable

Figure 25. Turnoff Enable

Figure 27. Output Voltage Ripple – FCCM

Figure 27. Output Voltage Ripple – FCCM

Figure 29. Load Transient – FCCM

Figure 29. Load Transient – FCCM

Figure 31. DE Mode DCM and CCM Transition

Figure 31. DE Mode DCM and CCM Transition

Figure 33. Overcurrent Protection

Figure 33. Overcurrent Protection

Figure 35. Overtemperature Protection

Figure 35. Overtemperature Protection

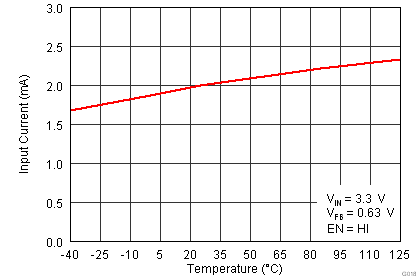

Figure 2. Input Current vs Temperature

Figure 2. Input Current vs Temperature

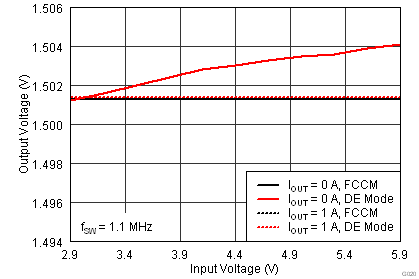

Figure 4. Output Voltage vs Input Voltage

Figure 4. Output Voltage vs Input Voltage

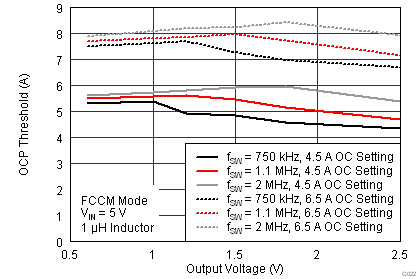

Figure 6. OCP Threshold vs Output Voltage

Figure 6. OCP Threshold vs Output Voltage

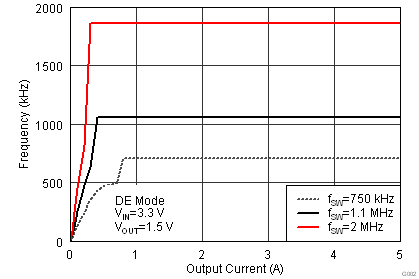

Figure 8. Frequency vs Output Current, DE Mode

Figure 8. Frequency vs Output Current, DE Mode

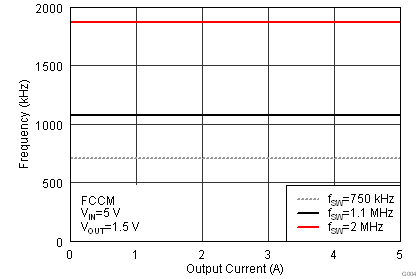

Figure 10. Frequency vs Output Current, FCCM

Figure 10. Frequency vs Output Current, FCCM

Figure 12. Frequency vs Output Current, HEF Mode

Figure 12. Frequency vs Output Current, HEF Mode

Figure 14. Efficiency vs Output Current, DE Mode

Figure 14. Efficiency vs Output Current, DE Mode

Figure 16. Efficiency vs Output Current, FCCM

Figure 16. Efficiency vs Output Current, FCCM

Figure 18. Efficiency vs Output Current, HEF Mode

Figure 18. Efficiency vs Output Current, HEF Mode

Figure 20. Efficiency vs Output Current, FCCM

Figure 20. Efficiency vs Output Current, FCCM

Figure 22. Efficiency vs Output Current, FCCM

Figure 22. Efficiency vs Output Current, FCCM

Figure 24. Prebiased Start-up

Figure 24. Prebiased Start-up

Figure 26. UVLO Start-Up Waveform

Figure 26. UVLO Start-Up Waveform

Figure 28. Output Voltage Ripple – DE Mode

Figure 28. Output Voltage Ripple – DE Mode

Figure 30. Load Transient – DE Mode

Figure 30. Load Transient – DE Mode

Figure 32. HEF Mode DCM and CCM Transition

Figure 32. HEF Mode DCM and CCM Transition

Figure 34. Short-Circuit Protection

Figure 34. Short-Circuit Protection