-

Alleviating Short Circuit Thermal Concerns for PoE Powered Devices

Alleviating Short Circuit Thermal Concerns for PoE Powered Devices

Alleviating Short Circuit Thermal Concerns for PoE Powered Devices

In IEEE 802.3bt Power over Ethernet (PoE) applications, an isolated power supply is implemented in most Power Devices (PDs) for safety considerations. In addition, DC-DC output overcurrent protection is an important topic especially end-equipment damage that creates an output short circuit condition. This paper introduces the thermal issues that can exist in a prolonged output short condition and how to alleviate any thermal concerns with discrete hiccup circuit. This circuit could be implemented in all of tps2375x family of PoE PDs.

Trademarks

All other trademarks are the property of their respective owners.

1 Introduction

In the traditional Flyback topology shown in Figure 1, the peak current signal is sensed through the current shunt resistor at the primary side of the power transformer. When the overcurrent occurs at output side, the Flyback controller IC will clamp the input current to the point of overcurrent protection (OCP) threshold by monitoring the peak current signal on current shunt resistor in Figure 2. The method of OCP protection is an input current limit, or input power (Pin) limit. That method also does output power (Pout) limit indirectly. During the OCP, based on Pout limit, the output voltage drops while the output peak fault current is increasing until the voltage on auxiliary (AUX) winding drops to hit the point of under voltage lockout (UVLO) of controller’s Vc pin. The worst case occurs at lower Vout and higher Pin limit at short circuit condition, producing the pretty high peak fault current and causing the thermal issue on Synchronous FET or Rectifying Diode at secondary side.

The duration of peak fault current depends on the capacitance on Vc pin of controller. The smaller capacitance on Vc pin, the higher hiccup OCP frequency is produced. The higher capacitance on Vc pin, the longer duration of peak fault current exists. Whatever the higher hiccup OCP frequency or the longer duration of peak fault current, the duty cycle of hiccup OCP is similar and the thermal issue could not be reduced. One way to minimize the thermal issue at short circuit condition is to reduce the hiccup OCP frequency and to make the shorter duration of peak fault current.

Figure 1. Traditional Flyback Current Limit Scheme

Figure 1. Traditional Flyback Current Limit Scheme  Figure 2. Peak current signal on current shunt resistor

Figure 2. Peak current signal on current shunt resistor 2 Detailed Description Using the TPS23754

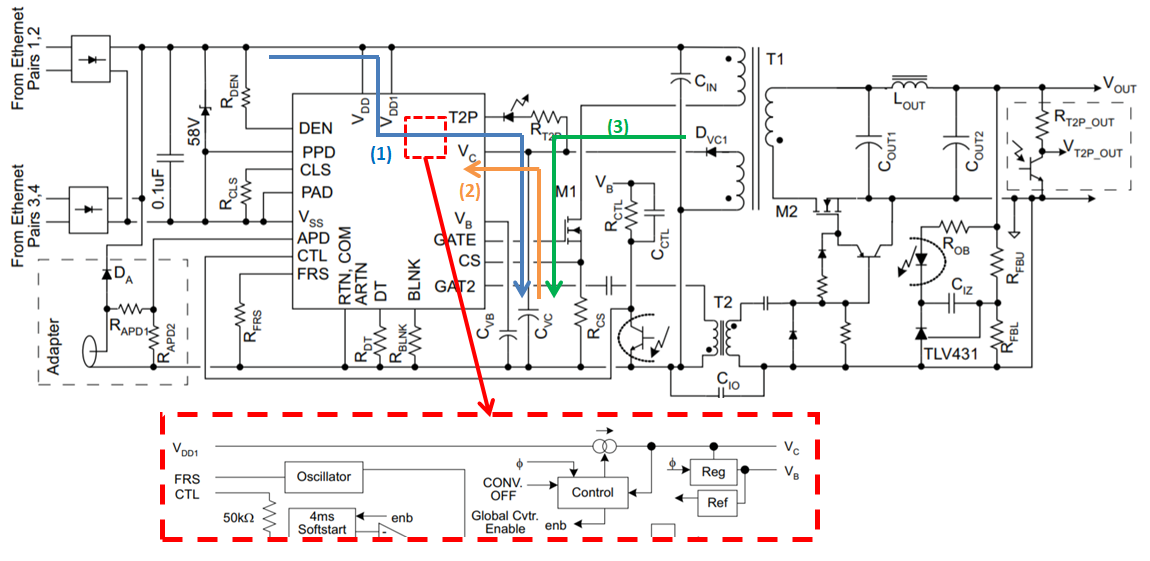

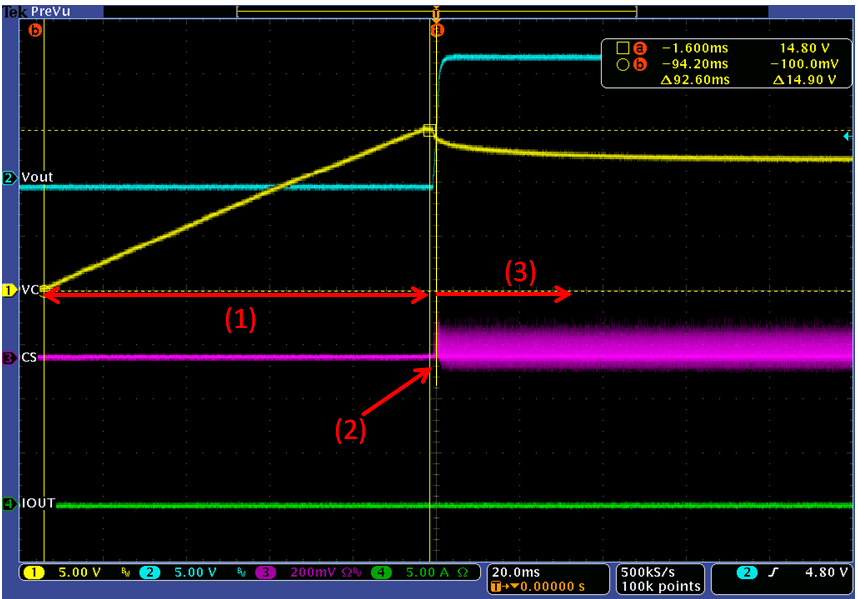

Figure 3 shows that when the standard PoE voltage range feeds VDD bus after PoE handshaking or adapter plug-in, the internal constant current source will be triggered to start charging the external Cvc capacitor. The voltage on Cvc is a constant rising slope until reaching to 15V,typ. The charging current path to external Cvc is (1). Therefore, the controller starts sending PWM pulse to switch the external primary FET M1 while the internal current source of controller is turned off. Before the output voltage (Vout) achieves the target Vout, the external Cvc capacitor is providing the energy as discharging to Vc pin as the source of the internal gate driver. The current path is (2). After Vout achieves the target voltage, the AUX winding start providing the energy to the internal gate driver and recharging Cvc capacitor. The current path is (3) and the waveform is shown in Figure 4.

Figure 3. Cvc Current Path During the Startup

Figure 3. Cvc Current Path During the Startup  Figure 4. Startup waveform on Cvc

Figure 4. Startup waveform on Cvc