-

Analyzing Butterfly-Style Footprint and Input Capacitor Removal Effects

Analyzing Butterfly-Style Footprint and Input Capacitor Removal Effects

Abstract

This application note delves into the unique symmetrical butterfly-style footprint of the TPS54KB2x, a highly efficient synchronous buck converter. Experimental data uncovers design intricacies and trade-offs, offering insights into the use for industrial and enterprise applications. The report explores how this footprint minimizes parasitics and the impact of removing input capacitors on one side of the IC package.

Trademarks

All trademarks are the property of their respective owners.

1 Introduction

The report objective is to interpret the distinctive butterfly-style footprint of the TPS54KB20 and how it is affected by removal of input capacitors from one side of the IC, resulting in an asymmetrical configuration. This particular buck converter falls under the TPS54KB2x device family, using an adaptive on-time D-CAP4 control mode, and supporting up to 25A of output current. TPS54KB2x's butterfly footprint proves to exhibit greater efficiency and enhanced device performance compared to its predecessor part. Considering users may seek the reduction of input capacitors to achieve further design flexibility, this device family allows the possibility of using a single VIN rail along with removing numerous input capacitors on one side of the IC package. This application note provides data on how further input capacitor reduction can affect efficiency and SW-node ringing during operation. Bench data is documented presenting SW-node ringing and efficiency results of the alternative input capacitor configuration. The report analyzes the TPS54KB20 SW-node ringing trade-offs when removing input capacitors asymmetrically on one side of the device, reducing area and cost. The data in this report refers to the TPS54KB20 U2 design EVM.

2 Butterfly Footprint Analysis

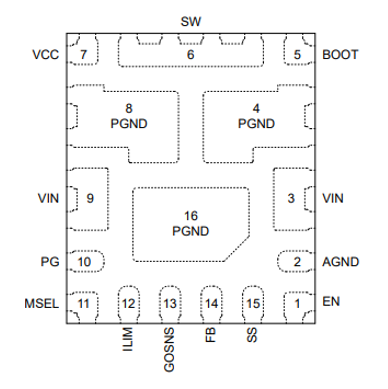

Figure 2-1 Butterfly-Style Outline

Figure 2-1 Butterfly-Style OutlineFigure 2-1 presents how the distinctive symmetrical layout appears in a pinout format. As previously mentioned, the footprint consists of two parallel VIN rails and two parallel PGND planes divided by the package symmetrically which aids in the reduction of parasitics. Furthermore, the butterfly footprint arranges the input capacitors in such a way that magnetic field cancellation occurs, leading to loop inductance being decreased.

Section 2.1 and Section 2.2 briefly show the efficiency and thermal advantages of TPS54KB20 compared to its predecessor part, TPS54JB20.