SLWU087E november 2013 – june 2023

- 1

- High Speed Data Converter Pro GUI

- Trademarks

- 1 Introduction

- 2 Software Start up

-

3 User Interface

- 3.1

Toolbar

- 3.1.1 File Options

- 3.1.2 Instrument Options

- 3.1.3 Data Capture Option

- 3.1.4

Test Options

- 3.1.4.1 Notch Frequency Bins

- 3.1.4.2 2 Channel Display and Cursor Lock

- 3.1.4.3 Analysis Window Markers

- 3.1.4.4 X-Scale in Time

- 3.1.4.5 Y-Scale in Voltage

- 3.1.4.6 Other Frequency Options

- 3.1.4.7 NSD Marker

- 3.1.4.8 Phase Plot

- 3.1.4.9 Phase in Degree

- 3.1.4.10 Histogram

- 3.1.4.11 Disable User Popups

- 3.1.4.12 HSDC Pro Lite Version

- 3.1.5 Help

- 3.2 Status Windows

- 3.3 Mode Selection

- 3.4 Device Selection

- 3.5 Skip Configuration

- 3.6 Capture Button (ADC Mode Only)

- 3.7 Test Selection (ADC Mode only)

- 3.8 DAC Display Panel (DAC Mode only)

- 3.9 I/Q Multi-Tone Generator

- 3.1

Toolbar

- 4 ADC Data Capture Software Operation

- 5 TSW1400 Pattern Generator Operation

- 6 TSW14J58 Functional Description

- 7 TSW14J57 Functional Description

- 8 TSW14J56 Functional Description

- 9 TSW14J50 Functional Description

- 10TSW14J10 Functional Description

- A Signal Processing in High Speed Data Converter Pro

- B History Notes

- C Revision History

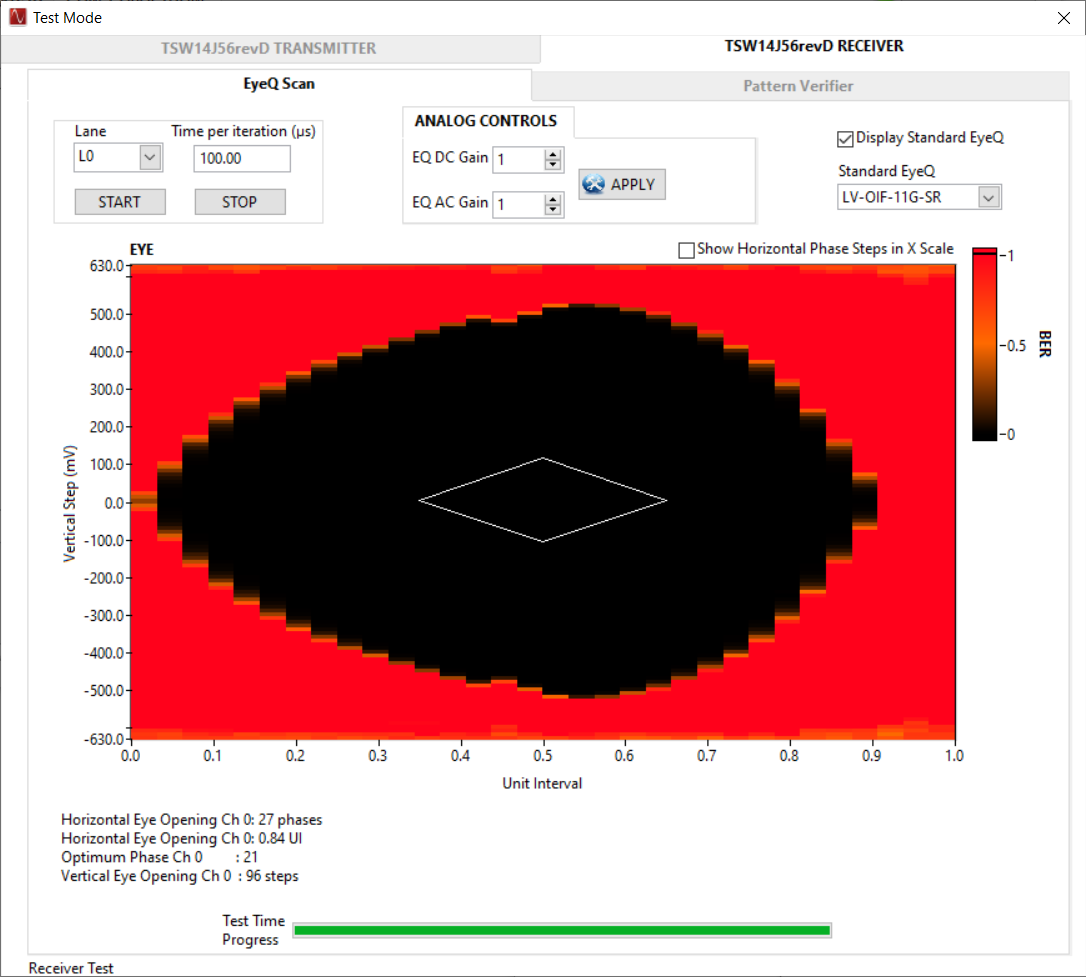

3.1.2.1 TSW14J56 and High Speed Data Converter (HSDC) Pro Eye Quality Analysis

The TSW14J56EVM uses an Intel PSG® Arria® V GZ FPGA device for the receive and transmit functions for the JESD204B link. One of the features of the Arria® V GZ device is the On-Chip Signal Quality Monitoring Circuitry (EyeQ). The EyeQ feature is a debug and diagnosis tool that analyzes the received data by measuring the horizontal and vertical eye opening.

The following section provides a quick start-up example that highlights the software features of the EyeQ Scan analysis.

- Verify that the ADC EVM provides an FFT capture on HSDC Pro.

- Under the "Instrument Options" tab, click on "SERDES Test Options".

- A new window should appear with the following features:

- Lane – Selects one of the available lanes for the selected interface mode

- Time per iteration – Selects how long data is accumulated before generation of the Eye diagram. Increasing this value also increases the Test Time proportionally

- EQ DC Gain – Adjusts DC gain of FPGA receive hardware block

- EQ AC Gain – Adjusts AC gain of FPGA receive hardware block

- Display Standard Eye – Overlays one of the JESD204B receive eye-mask templates onto the Eye diagram

- After configuring the parameters, click on "START". The scan may take a few seconds to a few minutes depending on the parameters chosen.

Figure 3-5 shows an eye diagram of the ADC34J45EVM in 442 mode, sampling at 140 MHz and a lane rate of 2.8 GHz.

Figure 3-5 Example Eye Diagram Plot

Figure 3-5 Example Eye Diagram Plot