Windowing, Sync, Sysref in LMX1205

Abstract

LMX1205 is a versatile clocking product which can act as multiplier, divider, and buffer. When LMX1205 is used in the signal chain and deterministic nature across the signal chain is needed, certain sequence of events have to be performed. This deterministic nature of clock bringup in signal chain helps in predictable JESD link and post processing following it. This app note covers the sequence of events to be followed to maintain the deterministic nature.

Trademarks

All trademarks are the property of their respective owners.

1 Introduction

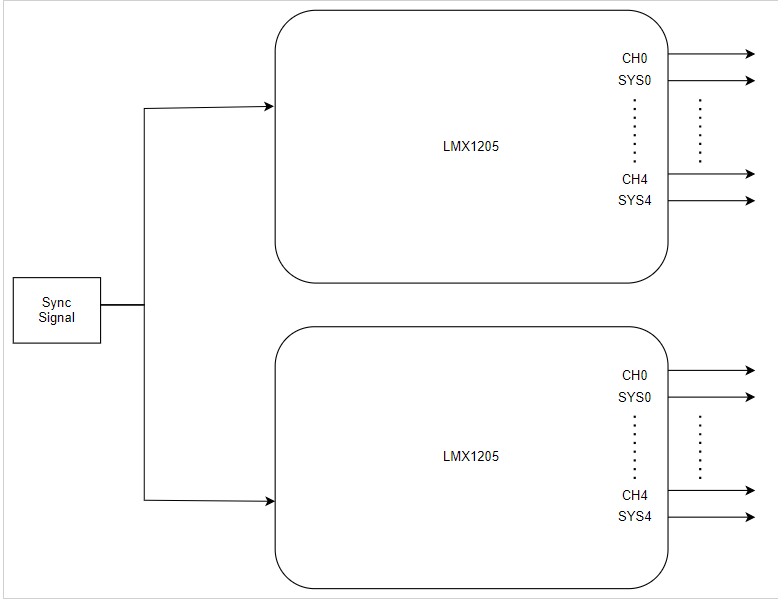

Block diagram of the LMX1205 outputs is shown in Figure 1-1. Consider a case, where LMX1205 is used as buffer/multiplier/divider in the clock path (CH0-CH3) and is required that all the channels (CH0-CH3) and sysref (SYS0-SYS3) need to be in sync and deterministic irrespective of the power supply toggling. This application note covers the steps to be followed to get that deterministic nature with lab measured waveforms using LMX1205 tics-pro. In general, sysref channels are low frequency clocks(<200MHz). Sync Signal is an external signal which can be both AC coupled and DC coupled. By default, it is AC coupled in LMX1205.

Figure 1-1 Sync Signal Driving Two LMX1205

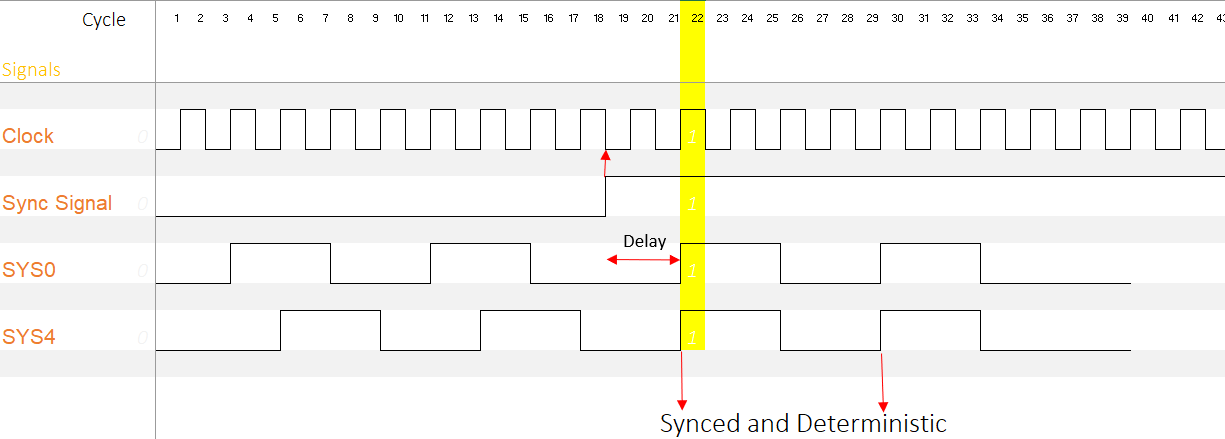

Figure 1-1 Sync Signal Driving Two LMX1205There are different modes of operation to be taken care before we see the final synced output, which is discussed in the subsequent sections. Assuming (as shown in Figure 1-2) somehow the Sync Signal rise edge is coming on the clock negative edge. After some delay, SYS0 and SYS4 are synced and deterministic. Absolute delay depends on the divider used for sysref path. But for a particular sysref divider settings, no matter how many power cycles done, it is always deterministic. This application note focus on using sysref outputs for explaining the concepts and same is applicable for other channel outputs also. If sync signal is not going from low to high in one input clock window to two LMX1205s, then determinism is not achievable.

Figure 1-2 Pre and Post Sync Waveform Illustration

Figure 1-2 Pre and Post Sync Waveform Illustration2 Where Does the Sync Signal Rise Come With Respect to the Clock Rise Edge?

To have reliable Sync operation, Sync signal needs to come on the fall edge of the clock. This can help avoid setup and hold regions of the flops inside LMX1205. What if the device generating the Sync signal do not have the option to delay the edge? Here comes the windowing feature. No matter where the Sync signal comes, windowing feature can help park this sync signal internally at the fall edge of the clock. Register(R18<5:0>, SYSREFREQ_DLY register) has to be written before doing sync operation whose value is obtained from windowing feature. In some cases, Sync signal can be periodic signal, which is internal multiple of clock period. In that case, on every low to high transition of Sync Signal, Syncing can happen. To stop that, there is an SYNC_STOP(R17<4>) option. If this bit is enabled, subsequent low to high transition on Sync Signal is ignored. All naming mentioned for the registers are as per the tics-pro Field names with tics-pro version 1.7.7.6.

As discussed previously, windowing needs to be done and then Sync. To enter into each of these modes, register have to be written as shown in Table 2-1.

| SYSREFREQ_MODE (R17<1:0>) | Mode of operation |

|---|---|

| 0 | Sync Mode |

| 1 | Request Mode(Default) |

| 2 | Windowing Mode |

When user is in Sync mode and Windowing mode, sysref signal is switched off. To get output from sysref, user has to enter Request mode post Windowing and Sync. Figure 1-2 waveforms, showing sysref output in sync mode, are just for illustration purpose of the sync feature.