SNAU246A June 2020 – January 2021 LMX2820

4.2.2 Offset Mixing With PFDIN Pin

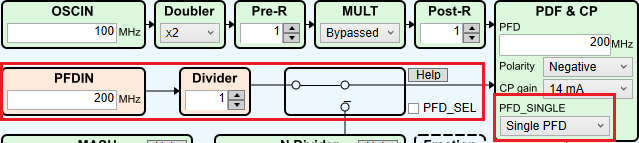

The LMX2820 supports offset mxing with PFDIN pin. In this mode, the internal N divider is bypassed.

When using offset mixing with PFDIN pin, the phase detector must operate with a single PFD. As a result, the charge pump current is equal to half the current setting made in register CPG.

Figure 4-4 Offset Mixing With PFDIN Pin

Setting

Figure 4-4 Offset Mixing With PFDIN Pin

Setting