SNAU288 December 2023 LMX1906-SP

4.1 Buffer, Divider, and Multiplier Modes

From the top-menu, click Default Configuration → 800 MHz Buffer Mode. This automatically loads the buffer mode profile.

Figure 4-1 Loading the Default Configuration

Figure 4-1 Loading the Default ConfigurationIf termination is not applied on all output pins, then manually disable the unused outputs using the CHx_EN fields (to completely power down unused channels) or the CLKOUTx_EN, SYSOUTx_EN, and LOGICLK_EN/LOGISYS_EN fields (to power down output buffers only). Powering down unused channels greatly reduces current consumption, and for the logic clocks in particular can reduce spurious interference.

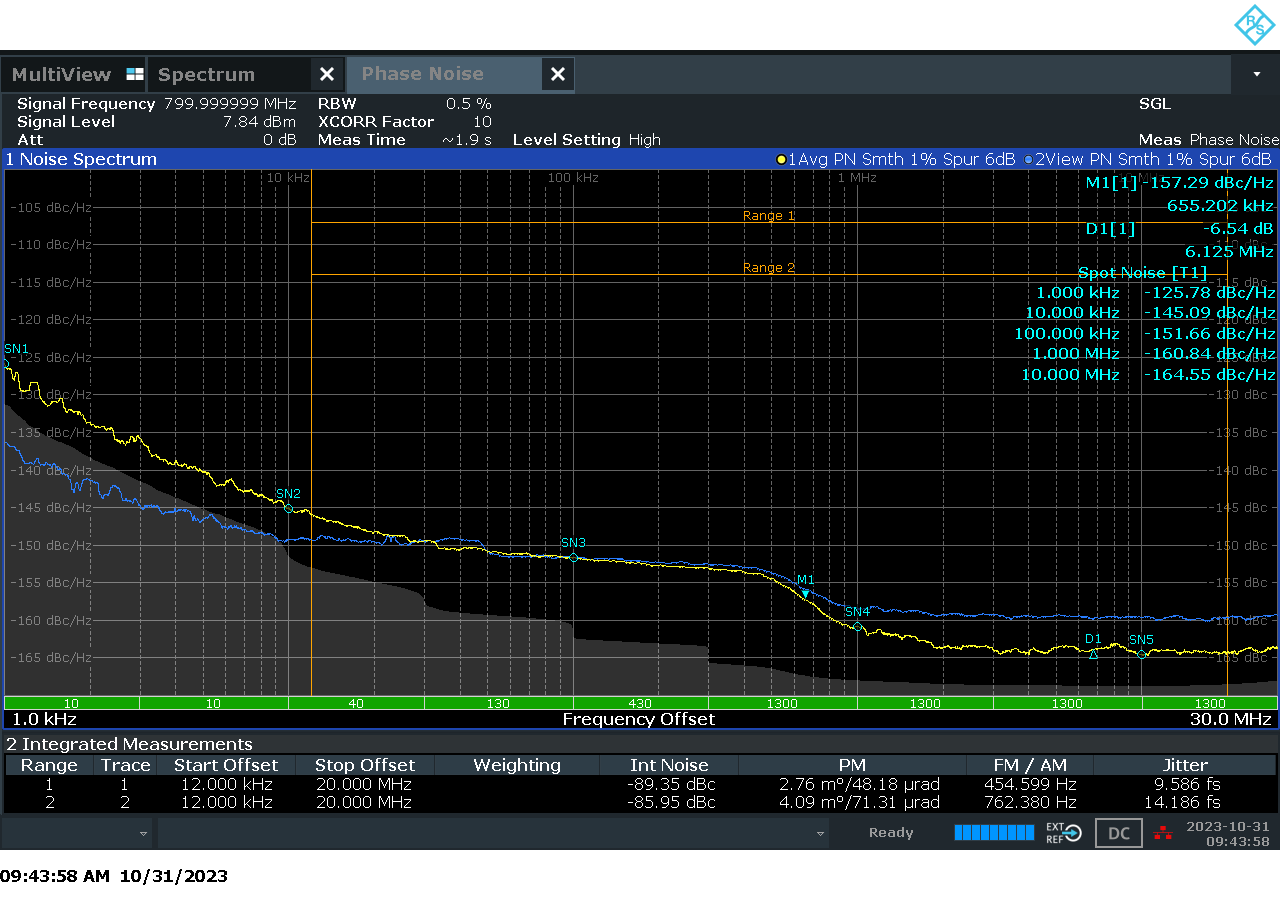

After the profile is loaded and required any changes have been made, the signal analyzer shows an 800-MHz signal at around +6-dBm single-ended, or +9-dBm differential.

The blue trace is the reference clock from SMA100B and the yellow trace is the 800 MHz buffered output.

Figure 4-2 800-MHz Buffer Mode Signal Analyzer Plot

Figure 4-2 800-MHz Buffer Mode Signal Analyzer PlotTo activate the multiplier or the divider, change the CLK_MUX field to specify divider or multiplier modes, and change the CLK_DIV and CLK_MULT fields to specify the frequency scaling factor. To make sure the device cleanly enters each mode, first, the desired configuration must be prepared in the GUI. Then, from the User Controls page the device must be reset by toggling the RESET field, and finally the registers must be reloaded using the USB Communications → Write All Registers menu option, or by pressing the accelerator keys CTRL + L.

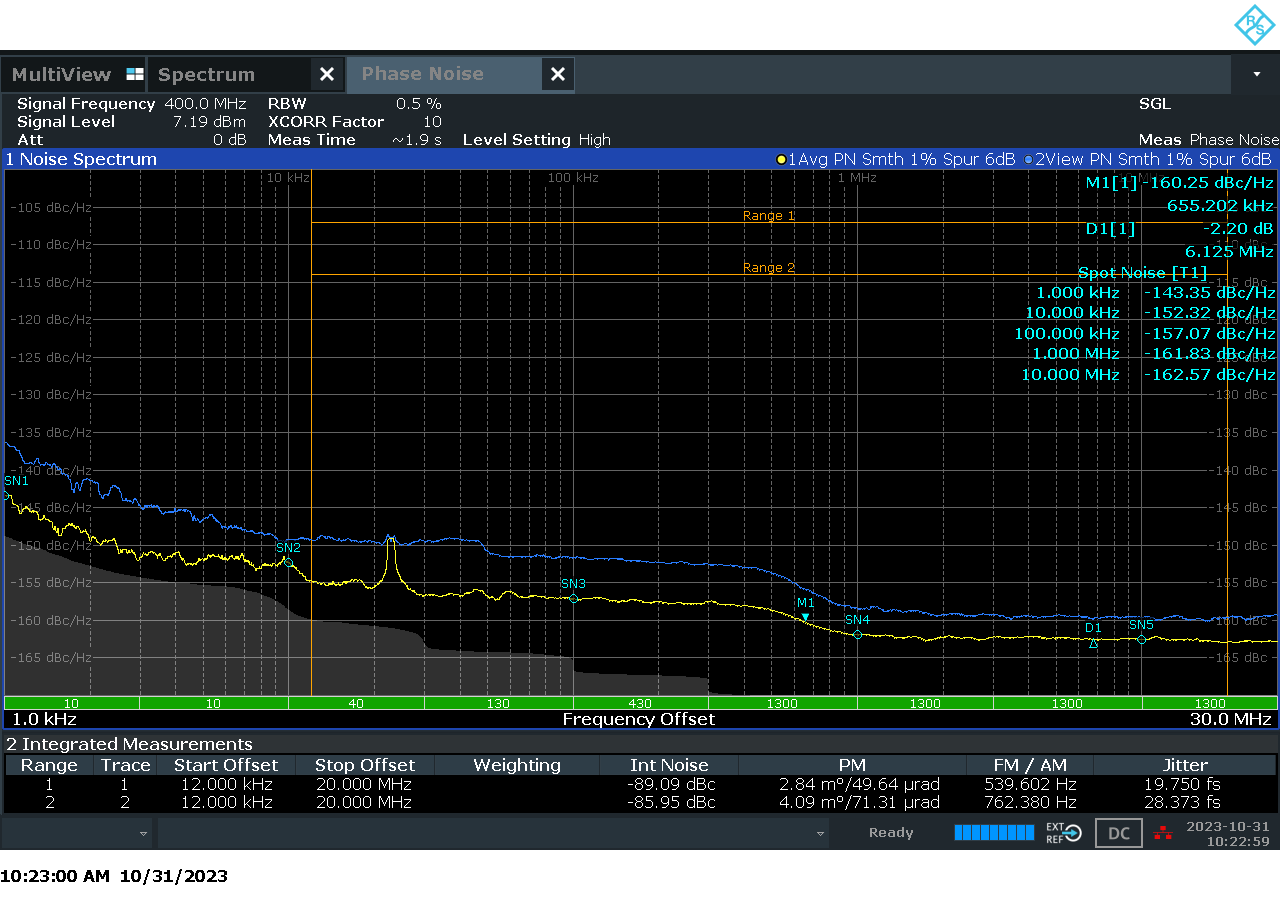

The yellow trace is the 400 MHz divided output.

Figure 4-3 800-MHz Divide-by-2 Mode Signal Analyzer Plot

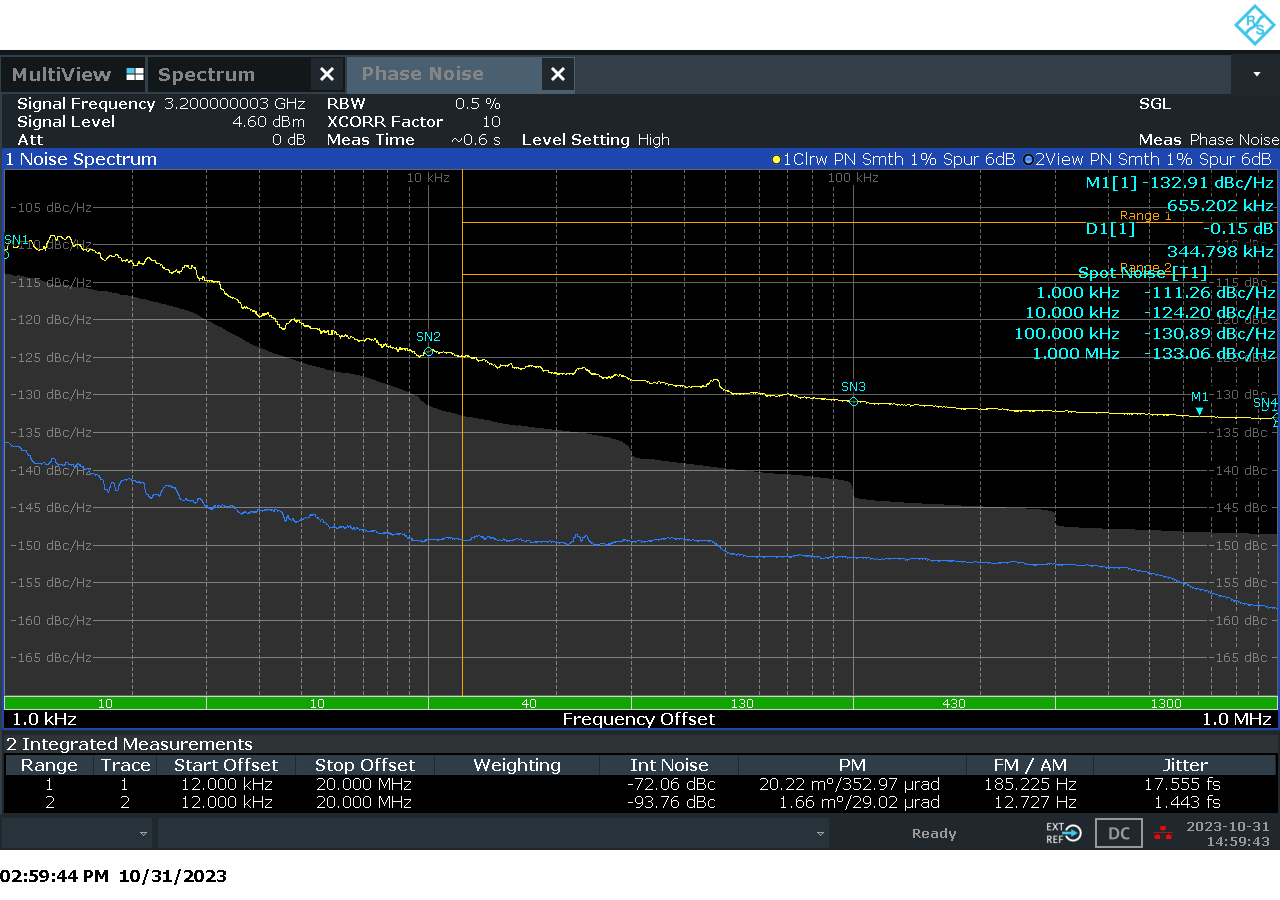

Figure 4-3 800-MHz Divide-by-2 Mode Signal Analyzer PlotThe yellow trace is the 3200 MHz output.

Figure 4-4 800-MHz Multiplier x4 Mode Signal Analyzer Plot

Figure 4-4 800-MHz Multiplier x4 Mode Signal Analyzer Plot