SNAU293 May 2024 LMX1860-SEP

- 1

- Description

- Features

- Applications

- 5

- 1Evaluation Module Overview

-

2Hardware

- 2.1

Setup

- 2.1.1 Evaluation Setup Requirement

- 2.1.2 Connection Diagram

- 2.1.3 How to Enable Full SPI Control

- 2.1.4 Power Requirements

- 2.1.5 Pin Mode Strapping

- 2.1.6 Reference Clock

- 2.1.7 Output Connections

- 2.1.8 Header Information

- 2.1.9 Default Configuration

- 2.1.10 How to Generate SYSREF

- 2.1.11 Multiplier Mode Example

- 2.1.12 Divider Mode Example

- 2.1.13 Hybrid Mode: SPI and Pin Mode

- 2.1

Setup

- 3Software

- 4Implementation Results

- 5Hardware Design Files

- 6Additional Information

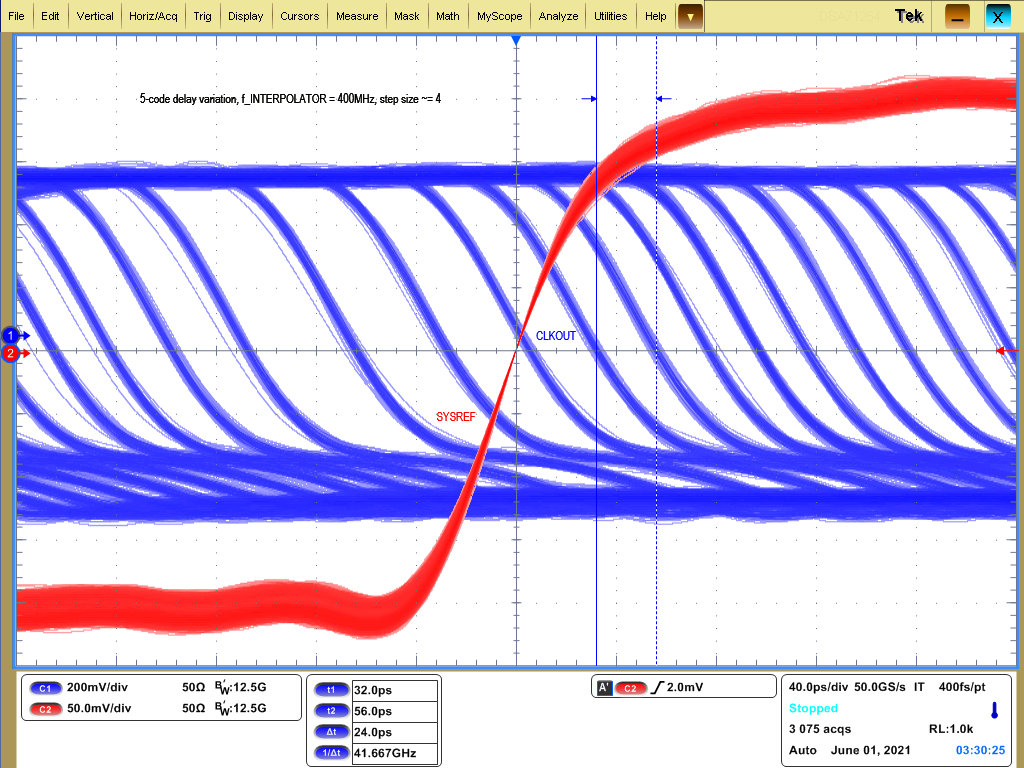

4.3 SYSREF Delay Generators

In generator modes, the SYSREF can be delayed by picosecond-size steps to more closely meet setup and hold requirements for high-frequency clock outputs. A delay divider, SYSREF_DELAY_DIV, generates the interpolator frequency fINTERPOLATOR, which is usually in the range of 400MHz to 800MHz. This interpolator frequency is further subdivided into 512 delay codes, allowing approximately 2.5ps to 5ps delay steps across most of the CLKIN frequency range.

Each channel has delay codes, which can be entered. The delay code algorithm is documented in the data sheet. To simplify delay calculation, the GUI provides an estimated relative delay: enter the relative delay, and the GUI calculates the correct step values to achieve the requested delay as closely as possible. Alternately, the register-based delay fields can be stepped through or programmed to achieve the same result.

Figure 4-6 SYSREF Delay in 5-Code Steps

Figure 4-6 SYSREF Delay in 5-Code Steps