SNLA448 November 2023 LMK3H0102

5.2 PCIe Tool Input File Waveforms for the LMK3H0102 Family

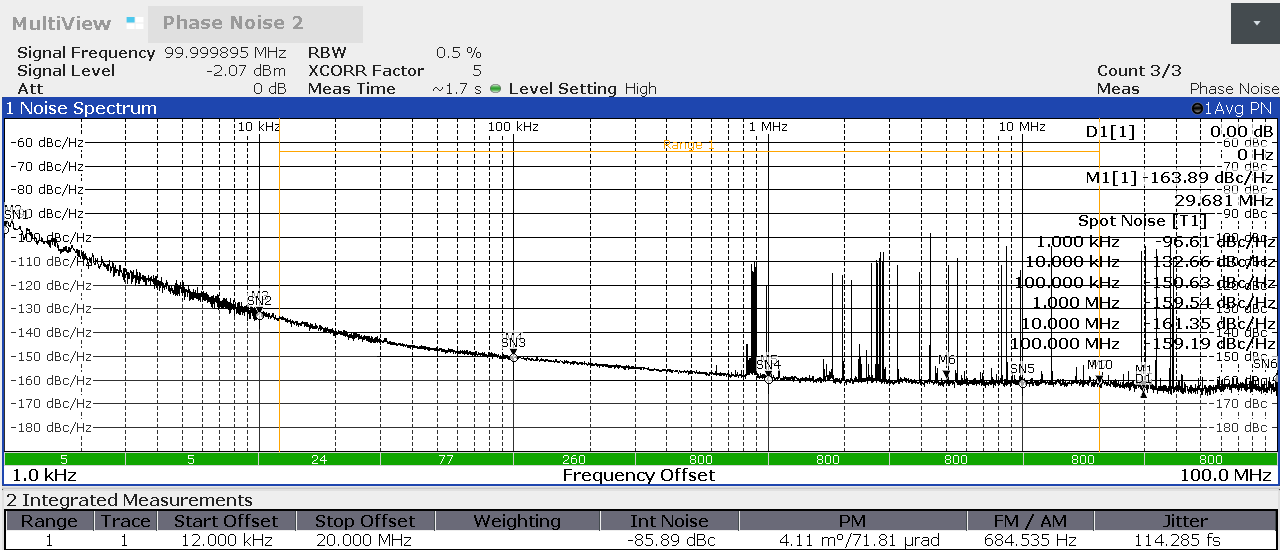

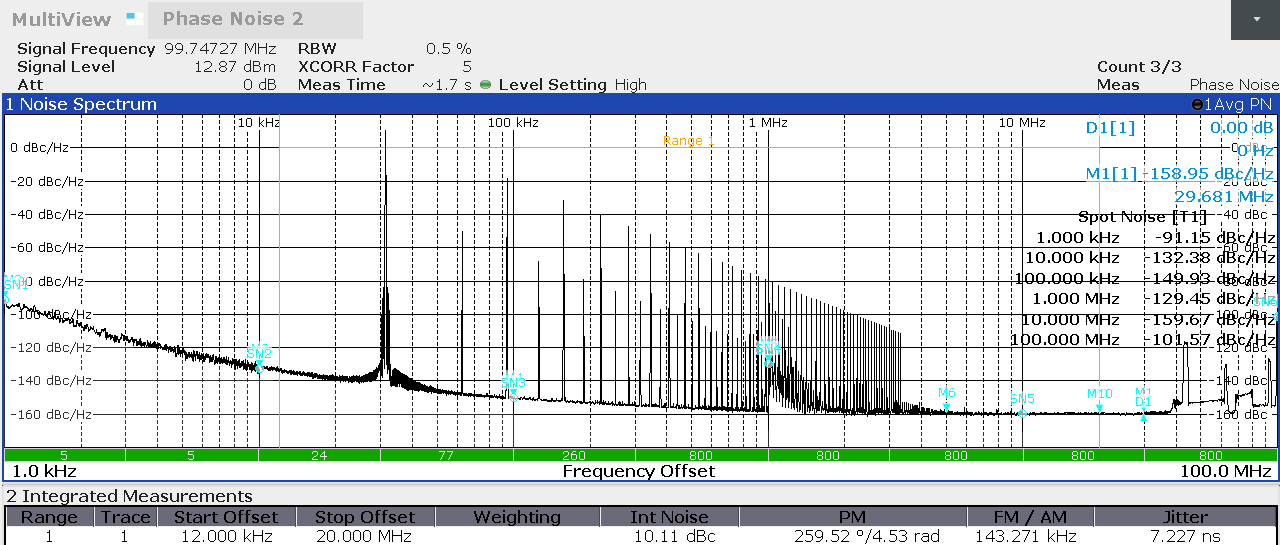

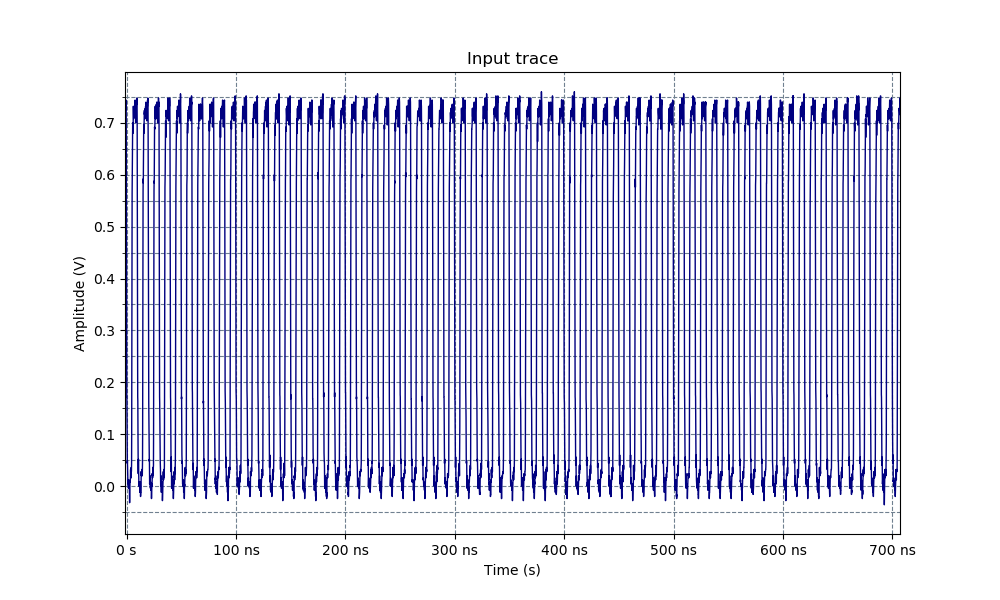

Figure 5-1 illustrates output phase noise curve of the LMK3H0102 with a 100-MHz LP-HCSL –0.5% down-spread SSC output.Figure 5-2 illustrates output phase noise curve of the LMK3H0102 with a 100-MHz LP-HCSL –0.5% down-spread SSC output. Figure 5-3 illustrates the input trace waveform. All of these waveforms are inputted into TI's PCIe Compliance Tool (found within TI's TICS Pro Software, more information in Section 4) to determine PCIe compliance.

Figure 5-1 Output Phase Noise Curve from

the LMK3H0102, 100-MHz LP-HCSL, No SSC

Figure 5-1 Output Phase Noise Curve from

the LMK3H0102, 100-MHz LP-HCSL, No SSC Figure 5-2 Output Phase Noise Curve from

the LMK3H0102, 100-MHz LP-HCSL, –0.5% Down-Spread SSC

Figure 5-2 Output Phase Noise Curve from

the LMK3H0102, 100-MHz LP-HCSL, –0.5% Down-Spread SSC Figure 5-3 Output Time Domain Plot from

the LMK3H0102

Figure 5-3 Output Time Domain Plot from

the LMK3H0102