SNVU890 January 2024

2.1.1.2 PWM Input

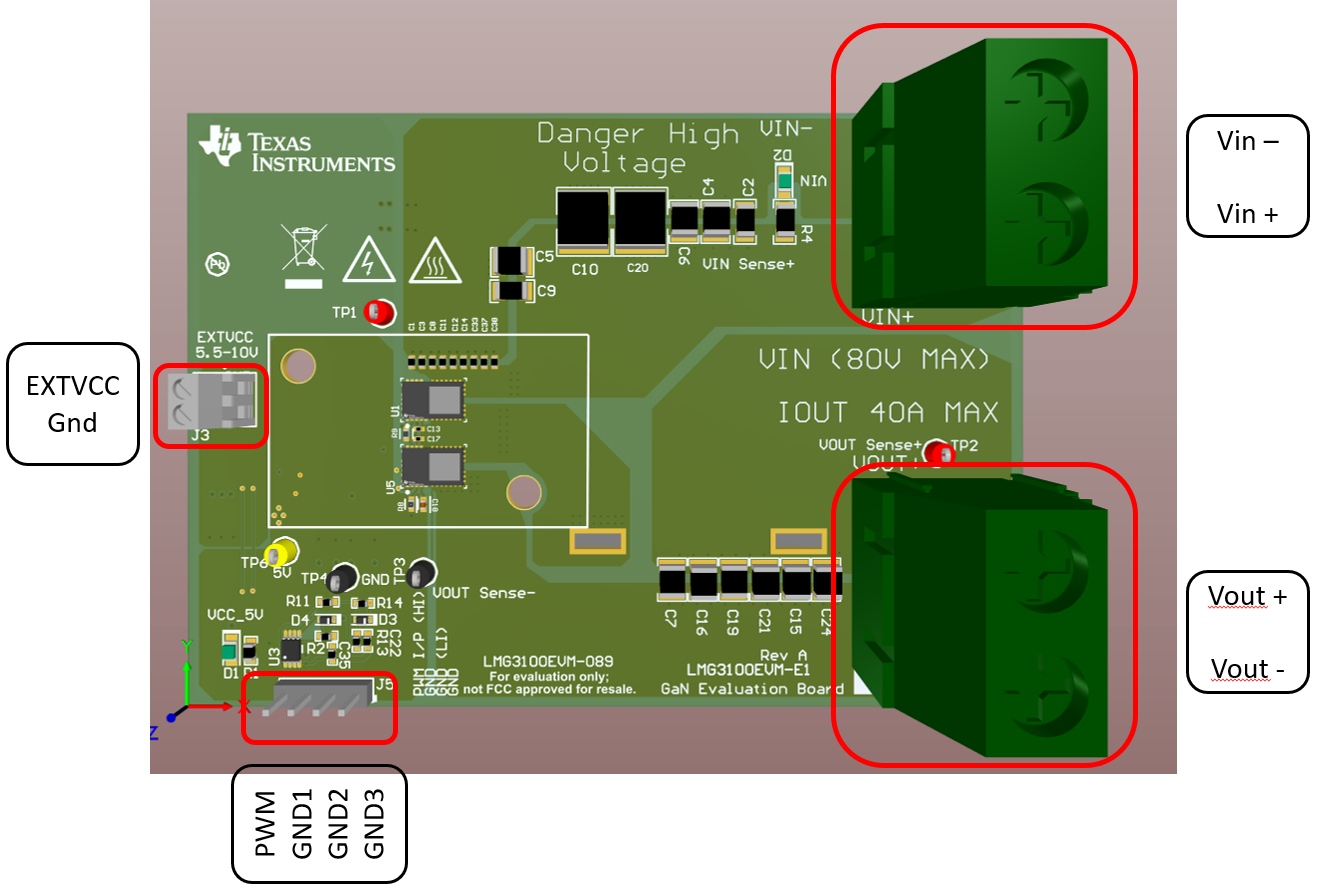

Provide the PWM input using a function generator that is capable of providing the desired switching frequency and duty cycle. This function generator output (0-5V signal) must be connected to the J5 connector as shown in the Figure 3-1. The left-most pin (pin 4) in this view is the positive input of the PWM supply and the remaining three pins are connected to GND in the default assembly for the board. The combination of R14-C22 and R2-C35 generate the dead time for the board. The combination can be adjusted to achieve the best deadtime for the chosen switching frequency.

Alternatively, two separate PWM inputs can be applied to control HI and LI independently. To apply this type of control, R11 must be removed, R13 must be populated with a 0-Ω resistor, and R12 must be replaced with a 10-kΩ resistor. On a board with these modifications, the HI signal must be applied at pin 4 (PWM) of J5, and the LI signal at pin 2 (GND 2) of J5. Note that with this control scheme, the EVM no longer generates a dead time separating HI and LI transitions. Therefore, careful consideration must be applied to the control signals in this mode of operation to prevent a shoot-through condition. When using the low side device to level shift the HI signal to control the high side FET there is an additional propagation delay of 35ns added to the high side signal. This must be considered when programming the deadtime externally. The on-board deadtime generation accounts for this by increasing the turn-on deadtime of the LO signal (R14-C22).

Figure 2-1 PWM Connection on

J5

Figure 2-1 PWM Connection on

J5