SPRAD06B March 2022 – November 2024 AM620-Q1 , AM623 , AM625 , AM625-Q1

- 1

- Abstract

- Trademarks

- 1Overview

-

2DDR4 Board Design and Layout Guidance

- 2.1 DDR4 Introduction

- 2.2 DDR4 Device Implementations Supported

- 2.3 DDR4 Interface Schematics

- 2.4 Compatible JEDEC DDR4 Devices

- 2.5 Placement

- 2.6 DDR4 Keepout Region

- 2.7 DBI

- 2.8 VPP

- 2.9 Net Classes

- 2.10 DDR4 Signal Termination

- 2.11 VREF Routing

- 2.12 VTT

- 2.13 POD Interconnect

- 2.14 CK and ADDR_CTRL Topologies and Routing Guidance

- 2.15 Data Group Topologies and Routing Guidance

- 2.16 CK and ADDR_CTRL Routing Specification

- 2.17 Data Group Routing Specification

- 2.18 Bit Swapping

-

3LPDDR4 Board Design and Layout Guidance

- 3.1 LPDDR4 Introduction

- 3.2 LPDDR4 Device Implementations Supported

- 3.3 LPDDR4 Interface Schematics

- 3.4 Compatible JEDEC LPDDR4 Devices

- 3.5 Placement

- 3.6 LPDDR4 Keepout Region

- 3.7 LPDDR4 DBI

- 3.8 Net Classes

- 3.9 LPDDR4 Signal Termination

- 3.10 LPDDR4 VREF Routing

- 3.11 LPDDR4 VTT

- 3.12 CK0 and ADDR_CTRL Topologies

- 3.13 Data Group Topologies

- 3.14 CK0 and ADDR_CTRL Routing Specification

- 3.15 Data Group Routing Specification

- 3.16 Byte and Bit Swapping

- 4LPDDR4 Board Design Simulations

- 5Appendix: AM62x ALW and AMC Package Delays

- 6Revision History

4.5.1 Simulation Setup

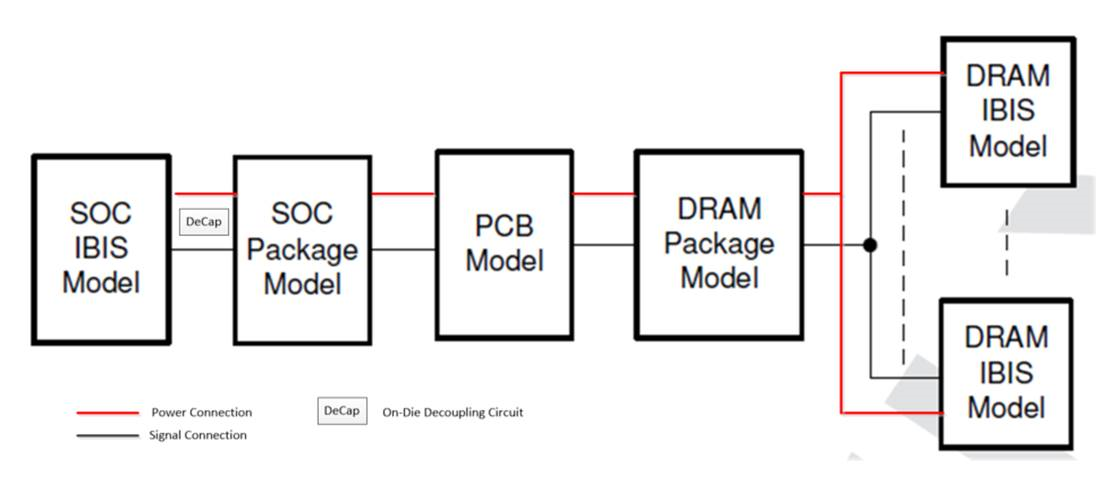

Set up the system-level schematic in the simulator by connecting the SOC IBIS model, board model, power supplies, DRAM package model, and DRAM IBIS model. A typical system-level DDR schematic is shown in Figure 4-2.

Note: Be aware of the DRAM

configuration (number of dies in the package, number of ranks, and

number of channels) while setting up the system schematic. Be aware

the DRAM configuration may also include On-Die Decoupling

Circuit.

Figure 4-2 Typical

System-Level DDR Schematic

Figure 4-2 Typical

System-Level DDR Schematic- LPDDR4 simulations require power-aware IBIS models for the controller and the memory along with a simulator that supports channel simulations for DDR interfaces.

- SPICE-based transistor-level simulations cannot be used for generating BER signal eyes. Use a simulator that can handle power-aware IBIS simulations and can run channel simulations for the DDR interface.

- IBIS models reduce simulation time with minimal loss in accuracy compared with SPICE-based transistor-level simulations. IBIS models starting from version 5.0 are power-aware models which enables Simultaneous Switching Output (SSO) noise simulations. The TI IBIS model is a power-aware IBIS model.

- Use SPICE models to accurately model the on-die decoupling capacitance on the DDR supply net for both – controller and DRAM. This ensures accurate power noise and Power Supply Induced Jitter (PSIJ) estimation in DDR simulations. The on-die decoupling capacitance information for the DRAM can be obtained from the DRAM vendor.

- Use SPICE or S-parameter files to model the DRAM package. This can be requested from the DRAM vendor. EBD models are not recommended.

- Note that inside the SoC IBIS model, there is a section for the package that contains an RLC matrix for all signal and power nets including DDR. It is recommended to use the SoC IBIS model, not the SOC package S-parameter model. When using SoC IBIS model, be sure to check the "Package Parasitics" (or equivalent parameter in your simulation tools) and use the "Package Model" model type which contains fully coupled L/C information on a per pin basis (denoted in the IBIS file as "[Package Model] am62_pkg").

- AM62x model for

the on-die decoupling capacitance on the DDR supply net:

- Data

****************************************** * On-die Decoupling circuit for AM62x (DIE_VDDS_DDR to VSS) ****************************************** * Notes: * Includes on-die decoupling for all DDR signals * * This subcircuit should be added across the AM62x IBIS model's * DIE_VDDS_DDR and VSS pins * ****************************************** * x_decouple DIE_VDDS_DDR vss_die AM62x_ondie_decoupling_alldq ****************************************** .SUBCKTAM62x_ondie_decoupling_alldq DIE_VDDS_DDR vss_die Cvddq_c DIE_VDDS_DDR DIE_VDDS_DDR_c 1.324741e-9 Rvddq_c vss_die DIE_VDDS_DDR_c 25.0036612e-3 .ENDS - Address/Command

****************************************** * On-die Decoupling circuit for AM62x (DIE_VDDS_DDR to VSS) ****************************************** * Notes: * Includes on-die decoupling for all DDR signals * * This subcircuit should be added across the AM62x IBIS model's * DIE_VDDS_DDR and VSS pins * ****************************************** * x_decouple DIE_VDDS_DDR vss_die AM62x_ondie_decoupling_alldq ****************************************** .SUBCKTAM62x_ondie_decoupling_alldq DIE_VDDS_DDR vss_die Cvddq_c DIE_VDDS_DDR DIE_VDDS_DDR_c 4.335517e-9 Rvddq_c vss_die DIE_VDDS_DDR_c 25.0036612e-3 .ENDS

- Data