SPRADG4A January 2024 – April 2024

- 1

- Abstract

- Trademarks

- 1General Texas Instruments High Voltage Evaluation (TI HV EVM) User Safety Guidelines

- 2Introduction

- 3System Description

- 4System Overview

- 5Hardware

-

6Software

- 6.1 Getting Started With Firmware

- 6.2 SysConfig Setup

- 6.3 Incremental Builds

- 7Testing and Results

- 8References

- 9Revision History

6.3.1.2.2 Overview of Lab 2

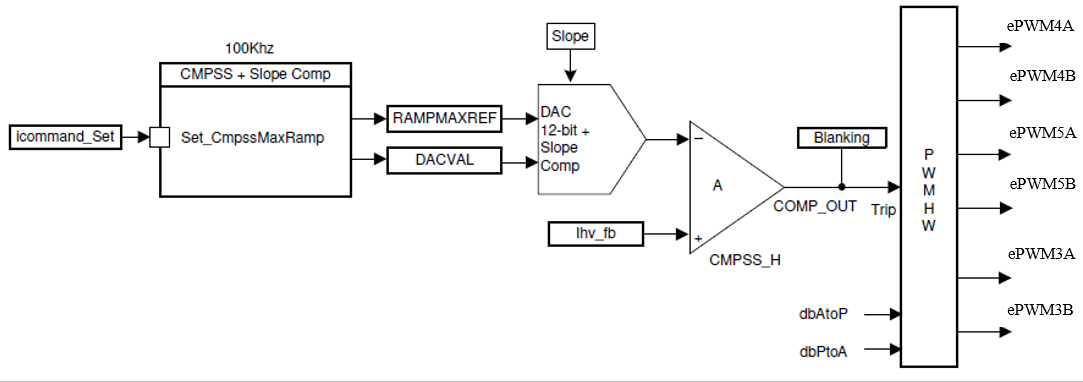

The software in lab 2 was configured so that the user can quickly evaluate the DAC driver module by viewing various waveforms on an oscilloscope and observing the effect of change in peak current reference command on the output voltage by interactively adjusting this command from CCS. The on-chip analog comparator compares the transformer primary current with the slope compensated peak current reference. Comparator output is connected to the trip zone logic of the PWM modules. ePWM4 module acts as the master time-base for the system. It operates in up-down count mode. ePWM4A and ePWM4B drive Q1 and Q4 full-bridge switches, while ePWM3A and ePWM3B drive Q2 and Q3 full-bridge switches. ePWM3A and ePWM3B drive Q5 and Q6 synchronous rectifier switches. Although the gating pulses for Q5 and Q6 are active, these switches do not start to operate unless 12V power supply is given to the base board through pin number 9 of J17 port. Whenever the comparator output goes high in a PWM half cycle, the ePWM3 module output (ePWM3A or ePWM3B) which was high at that instant is immediately pulled low while the other PWM3 module output is pulled high after an appropriate dead-band window (dbAtoP). ePWM5A and ePWM5B outputs are driven in a similar way. Note that this slope compensation ramp generation, comparator action and PWM waveform generation are all hardware generated without any software involvement as shown in Figure 6-9. Some register reconfigurations for SR are done inside the ISR.

Figure 6-9 Lab 2 Software Blocks

Figure 6-9 Lab 2 Software Blocks