SPRADG4A January 2024 – April 2024

- 1

- Abstract

- Trademarks

- 1General Texas Instruments High Voltage Evaluation (TI HV EVM) User Safety Guidelines

- 2Introduction

- 3System Description

- 4System Overview

- 5Hardware

-

6Software

- 6.1 Getting Started With Firmware

- 6.2 SysConfig Setup

- 6.3 Incremental Builds

- 7Testing and Results

- 8References

- 9Revision History

6.1.3 Project Folder Structure

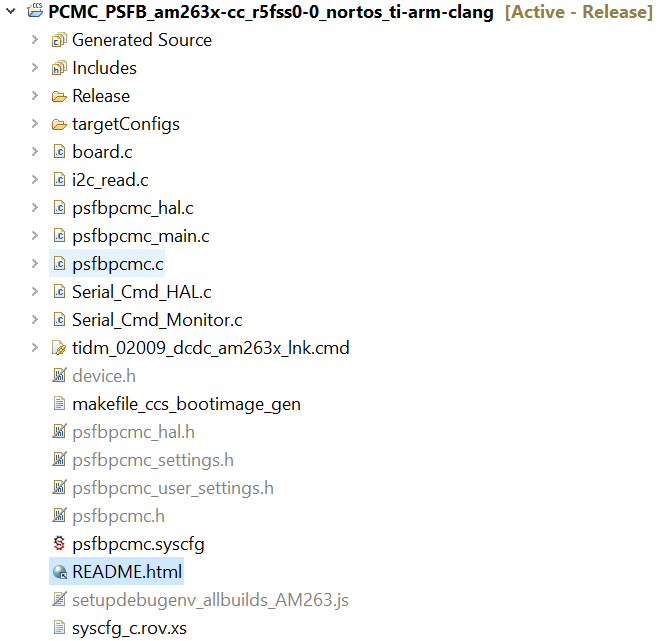

Project Structure shows the general structure of the project. Once the project is imported, the Project Explorer appears inside CCS.

Design-specific and device-independent files that consist of the core algorithmic code are in the Source folder. Library and Control Algorithms related to Digital Power Applications are present in the libraries folder. Board specific and Driver specific changes are configured in SysConfig and this code is automatically generated by SysConfig in the Release/SysCfg folder. The main.c file consists of the main framework of the project. This file consists of calls to the board and file that helps create the system framework, along with the interrupt service routines (ISRs) and slow background tasks. Figure 6-3 explains a detailed folder structure.

Figure 6-3 Project Structure

Figure 6-3 Project StructureAll variables and function calls are prepended by the PSFB name (for example, PSFB_vLVBus_sensed_pu). This naming convention lets the user combine different designs while avoiding naming conflicts.