SPRADH0 August 2024 AM625 , AM6442 , AM69 , TDA4VM

- 1

- Abstract

- Trademarks

- 1Introduction

- 2Evaluation Platform and Methods

- 3Performance Metrics

- 4Optimizations

- 5Summary

- 6References

- 7Appendix A: How to Setup TI Embedded Processors as EtherCAT Controller Using the CODESYS Stack

- 8Appendix B: How to Enable Unlimited Runtime on CODESYS Stack

4.2 Future Considerations

There are several additional steps to gain better visibility into why the CODESYS EtherCAT stack is affecting the CPU load and KPI as described in the previous section. These steps have not yet been extensively investigated but are described here as potential future steps to take. Many of these steps are based on suggestions given on the CODESYS Optimization for Linux Systems resource.

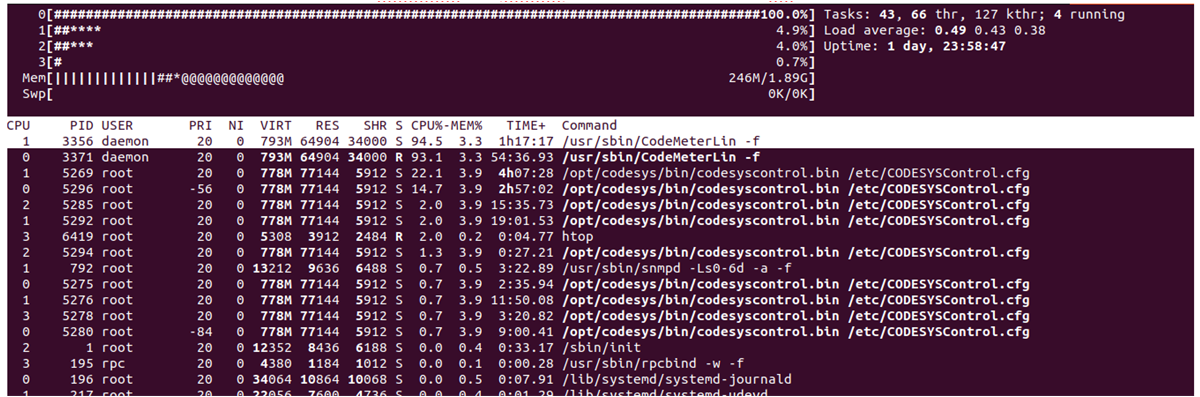

The optimizations described in the previous section are predominately discovered through experimentation. What is currently known is that when the CODESYS application is started on each hardware platform, a list of several threads related to the application appear. Figure 4-9 shows an example of this observation using an htop capture. This htop is taken during the time the Codemeter application caused a spike in CPU load. CODESYS documentation refers to these threads as “IEC tasks”.

The thread with priority -56 is specifically the EtherCAT task scheduled with a FIFO priority scheme. This can be verified by checking on the CODESYS Development System and the associated priority found on the CODESYS Mapping of Task Priorities on a Linux System resource. Understanding the function of the other CODESYS threads (“IEC tasks”) is more difficult.

Figure 4-9 CODESYS Related Threads on AM62x

Figure 4-9 CODESYS Related Threads on AM62xTo gain more visibility, the following steps can be taken:

Enable kernel tracing (ftrace) to detect if an interrupt or another service can be interfering with the performance of the EtherCAT task

Implement CPU load tracing object in CODESYS Development System for better granularity of CPU load over time

Run cyclictest while CODESYS EtherCAT application is running in the background to see if the metrics significantly differ from cyclictest running with stress-ng. The motivation for doing this task is to see if the metrics match up with EtherCAT cycle time and to see if the maximum latencies increased in a that is way indicative of large amounts of ethernet traffic.

Other experiments to try include the following. Keep in mind that for each experiment, first testing the results using cyclictest can be beneficial compared to the more extensive process of capturing data from CODESYS.