SPRADH9 June 2024 AM6442

- 1

- Abstract

- Trademarks

- 1Abbreviations

- 2Introduction

- 3X86 as RC and AM64x as EP

- 4Test Setup

-

5PCIe Test Specification

- 5.1 Identification and Configuration Functionalities

- 5.2 Reference Clock Functionalities

- 5.3 Inbound ATU and BAR Functionalities

- 5.4 Outbound ATU Functionalities

- 5.5 MSI Functionality

- 5.6 Downstream Interrupt Functionality

- 5.7 Device Power Management State Functionality

- 5.8 Function Level Reset Mechanism

- 5.9 Legacy Interrupt Mechanism

- 5.10 MSI-X Capability

- 5.11 Hot Reset Mechanism

- 6Windows Example Driver Verification

- 7References

5.3 Inbound ATU and BAR Functionalities

Test

Description:

Test to verify if PCIe inbound ATU and BAR configurations work correctly for the TMDS243EVM/TMDS64EVM PCIe EP.

By default, the following BAR configurations are set in Sysconfig for the pcie_enumerate_ep example application:

- Inbound Address Translation 0:

This ATU configuration uses region index 0 with a 32 Kbyte non-prefetchable 32bit memory BAR linked to an external struct bar0_mem. This inbound ATU configuration can not be modified for this test as it is required to ensure functionality with the RC VFIO based sample application ti-sample-vfio. - Inbound Address Translation 1:

This ATU configuration uses region index 1 with a 64 Mbyte prefetchable 32bit memory BAR linked to an external data buffer bar1_data. This inbound ATU may be modified for this test as it is specifically implemented to test various BAR configurations. - Inbound Address Translation 2:

This ATU configuration uses region index 2 with a 1 Gbyte non-prefetchable 64bit memory BAR linked to an external data buffer bar2_data. This inbound ATU may be modified for this test as it is specifically implemented to test various BAR configurations.

Execution:

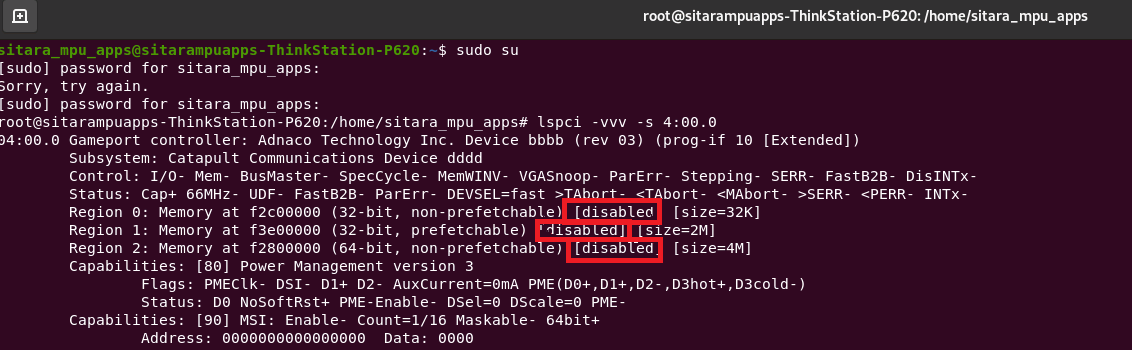

- Set desired BAR configurations in Sysconfig file for Inbound Address Translation 1 and 2 for pcie_enumerate_ep application.

- Check if desired PCIe EP BARs are configured

correctly on Linux-based RC hardware. On boot up the configured BARs can be

shown as disabled on PCIe configuration space as shown in the following

figure:

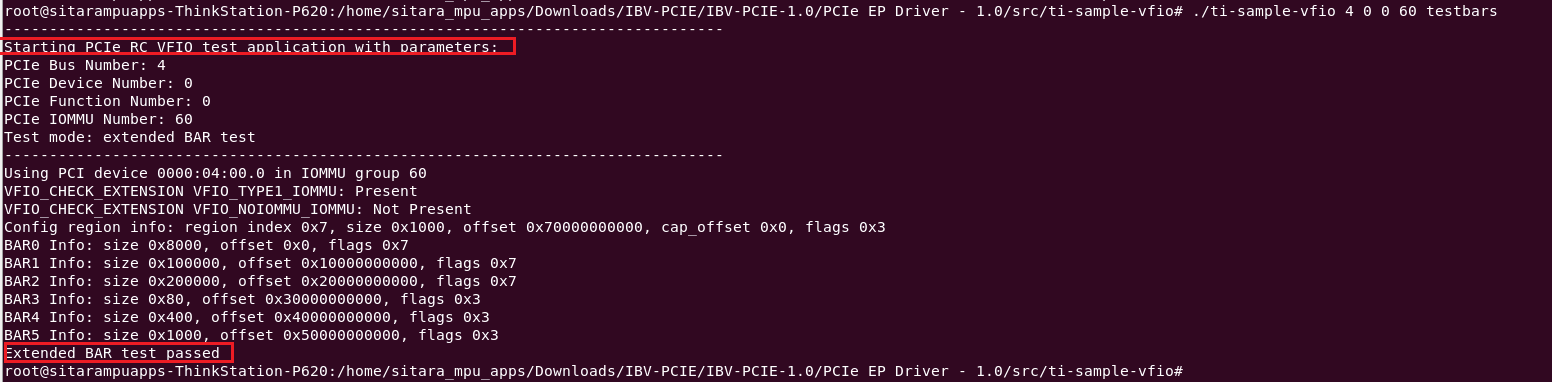

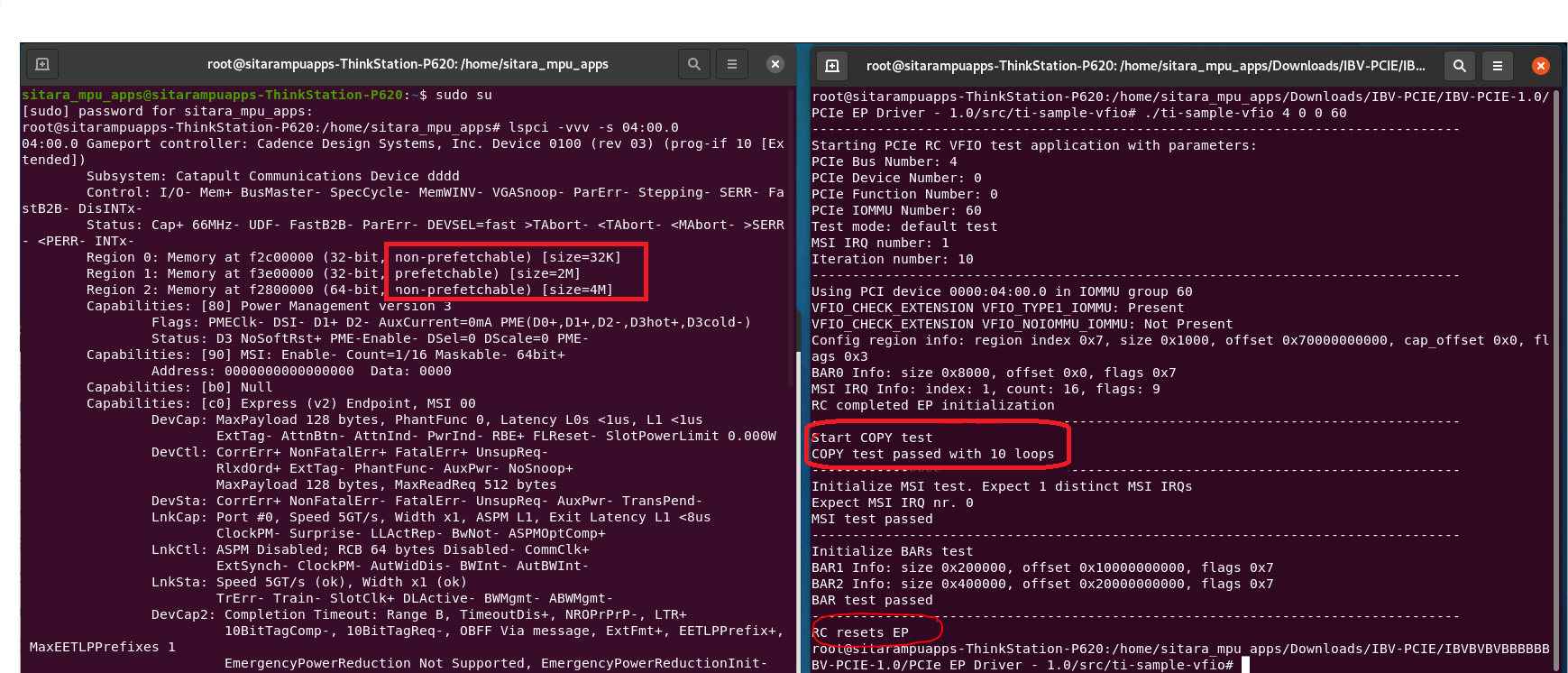

- Run RC sample application ti-sample-vfio.

Open a second Linux terminal and check PCIe EP configuration space. As the

program halts after EP initialization and BAR mapping, corresponding BARs can

now be enabled (not shown as disabled).

- Continue RC sample application

ti-sample-vfio. The program can continue normally and end without any

failure.

Test

Description

Test to verify if PCIe inbound ATU and extended BAR configurations work correctly for the TMDS243EVM/TMDS64EVM PCIe EP.

For this purpose, up to 6 different BAR configurations are defined for the PCIe EP:

- Inbound Address Translation 0:

This ATU configuration uses region index 0 with a 32 Kbyte non-prefetchable 32bit memory BAR. - Inbound Address Translation 1:

This ATU configuration uses region index 1 with a 32 Mbyte prefetchable 32bit memory BAR. - Inbound Address Translation 2:

This ATU configuration uses region index 2 with a 512 Mbyte non-prefetchable 32bit memory BAR. - Inbound Address Translation 3:

This ATU configuration uses region index 3 with a 128 byte 32bit I/O BAR. - Inbound Address Translation 4:

This ATU configuration uses region index 4 with a 1 Kbyte 32bit I/O BAR. - Inbound Address Translation 5:

This ATU configuration uses region index 5 with an 8 Kbyte 32bit. I/O BAR.

Execution:

- Set described BAR configurations in Sysconfig file for pcie_enumerate_ep application.

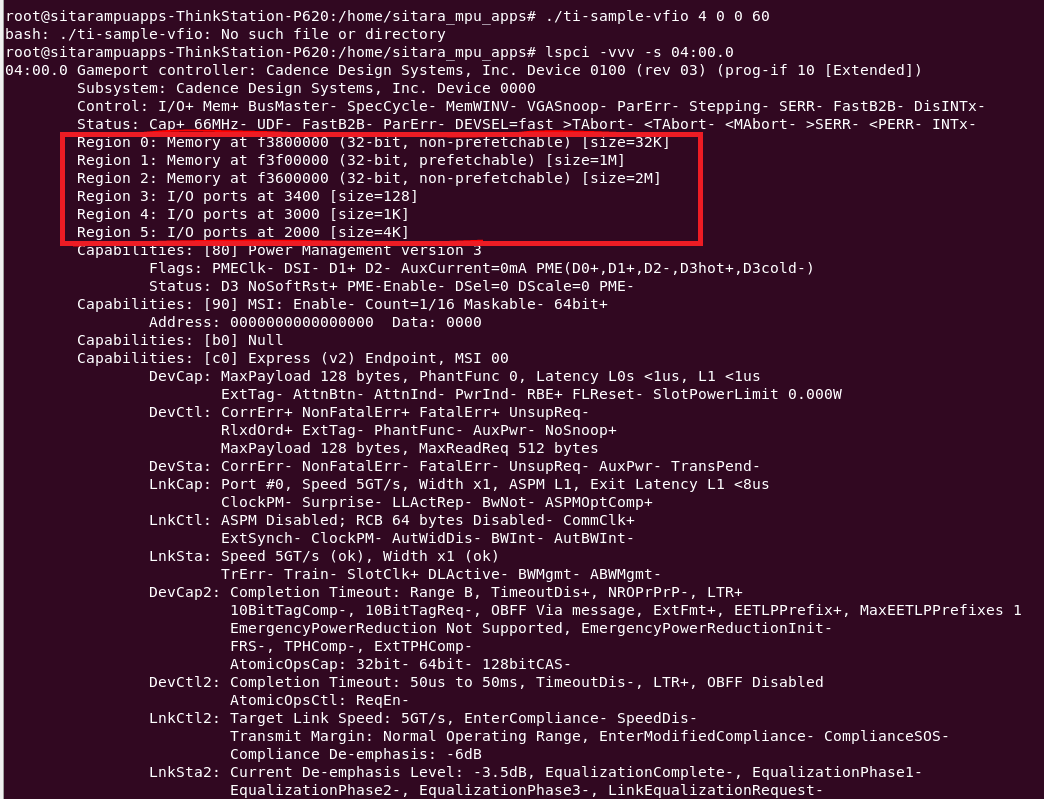

- Check if desired PCIe EP BARs are configured

correctly on Linux-based RC hardware. On boot up the configured BARs can be

shown as disabled on PCIe configuration space as shown in the following

figure:

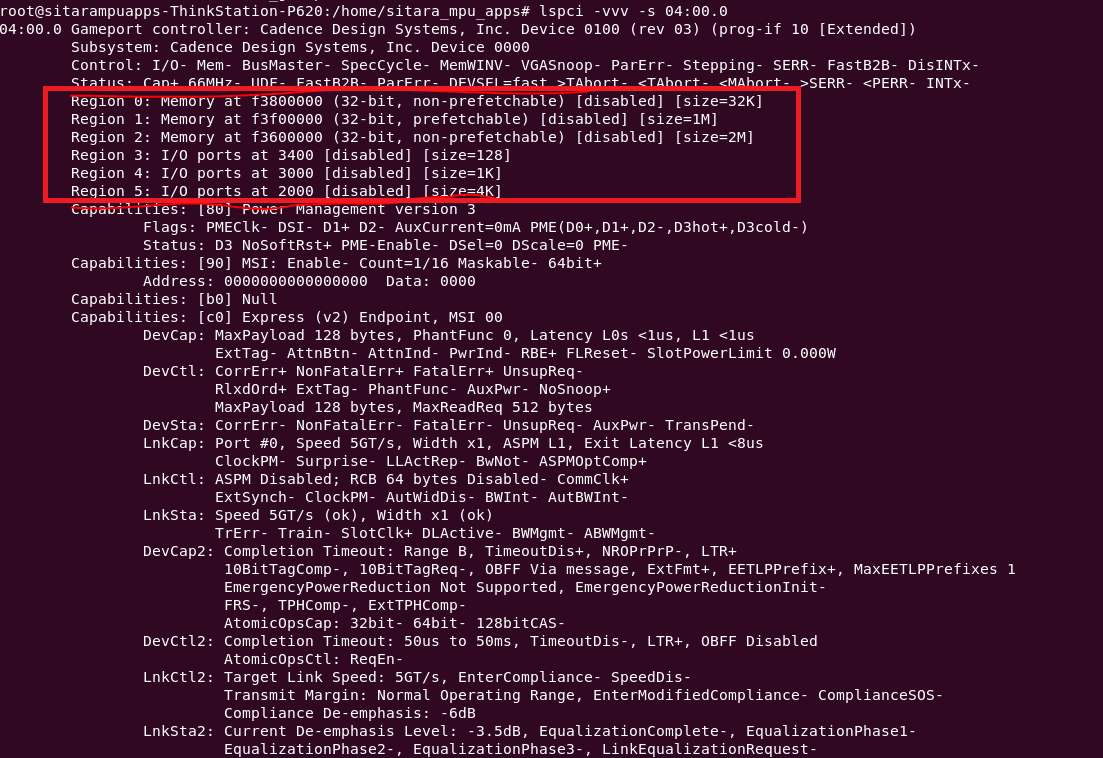

- Run RC sample application ti-sample-vfio

with parameter testbars. Open a second Linux terminal and check PCIe EP

configuration space. As the program halts after VFIO initialization,

corresponding BARs can now be enabled (not shown as disabled) as shown in the

following figure.

- Continue RC sample application

ti-sample-vfio. The program can perform an extended BAR test and

output BAR information as shown in the following figure.