SPRADH9 June 2024 AM6442

- 1

- Abstract

- Trademarks

- 1Abbreviations

- 2Introduction

- 3X86 as RC and AM64x as EP

- 4Test Setup

-

5PCIe Test Specification

- 5.1 Identification and Configuration Functionalities

- 5.2 Reference Clock Functionalities

- 5.3 Inbound ATU and BAR Functionalities

- 5.4 Outbound ATU Functionalities

- 5.5 MSI Functionality

- 5.6 Downstream Interrupt Functionality

- 5.7 Device Power Management State Functionality

- 5.8 Function Level Reset Mechanism

- 5.9 Legacy Interrupt Mechanism

- 5.10 MSI-X Capability

- 5.11 Hot Reset Mechanism

- 6Windows Example Driver Verification

- 7References

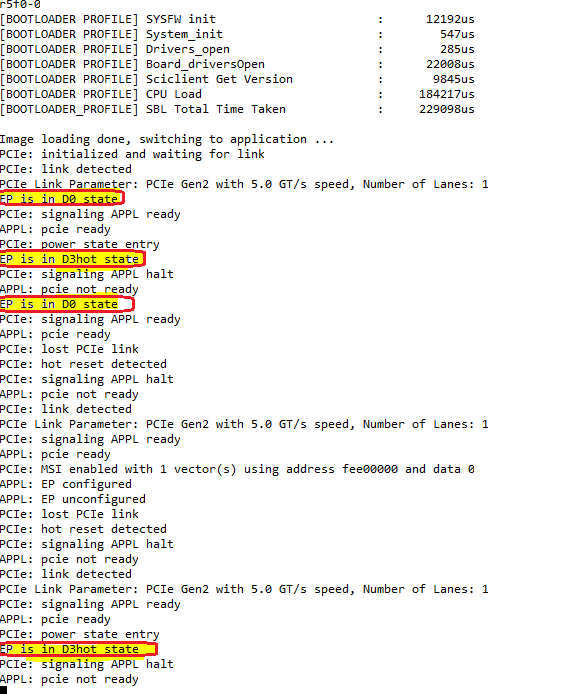

4.4.1 UART Console Output

Running the sample application puts the device from D3hot into D0 state.

The application outputs further state changes while the sample executes until finally the EP is put back into D3hot state:

EP is in D0 state

PCIe: signaling APPL ready

APPL: pcie ready

PCIe: lost PCIe link

PCIe: hot reset detected

PCIe: signaling APPL halt

APPL: pcie not ready

PCIe: link detected

PCIe Link Parameter: PCIe Gen2 with 5.0 GT/s speed, Number of Lanes: 1

PCIe: signaling APPL ready

APPL: pcie ready

PCIe: MSI enabled with 1 vector(s) using address fee00538 and data 0

APPL: EP configured

APPL: EP unconfigured

PCIe: lost PCIe link

PCIe: hot reset detected

PCIe: signaling APPL halt

APPL: pcie not ready

PCIe: link detected

PCIe Link Parameter: PCIe Gen2 with 5.0 GT/s speed, Number of Lanes: 1

PCIe: signaling APPL ready

APPL: pcie ready

PCIe: power state entry

EP is in D3hot state

PCIe: signaling APPL halt

APPL: pcie not ready