SPRADI9 June 2024 AM623 , AM625

- 1

- Abstract

- Trademarks

- 1Introduction

- 2Design-Based Approach

- 3Background

- 4Comparison of Design-Based Approach vs. HTOL Approach

- 5AM625/623 Lifetime Reliability Analysis Results

- 6Conclusion

- 7Revision History

- A Appendix – The HTOL-Based Approach

- B Appendix – The Mathematic Basis for EM Reliability Estimates

4 Comparison of Design-Based Approach vs. HTOL Approach

A well-engineered HTOL stress plan must adequately assess lifetime for TDDB mechanisms (e.g. GOI, ILD failure) in most cases. This can also include detection of extrinsic defects causing premature TDDB failure. In many cases, TDDB mechanisms are not ultimately the limiting factors for lifetime reliability.

Channel Hot Carrier (CHC) and Electromigration are generally not significantly accelerated during HTOL, even under dynamic stress conditions (the norm for processors). In the case of CHC, clock rates and slew conditions during the (dynamic) HTOL stress are not normally conducive to accelerated CHC degradation. Biased Thermal Instability (BTI) can be accelerated in HTOL, largely due to high temperature and voltage, but the dynamic switching activity that occurs during HTOL on the worst-case circuits can not sufficiently represent functional use condition, especially when considering overall aging can combine BTI and CHC components.

Electromigration current densities (also a strong function of clock rate), during HTOL bias are generally not high enough to demonstrate to 10+ years of lifetime when de-rated from a typical 1000-2000hr test duration (even at elevated voltage). Much longer durations are needed. Typically, structural stress patterns (i.e. ATPG-based) are applied with HTOL, along with memory or other applicable BIST, and clocking is normally well below maximum operating frequency.

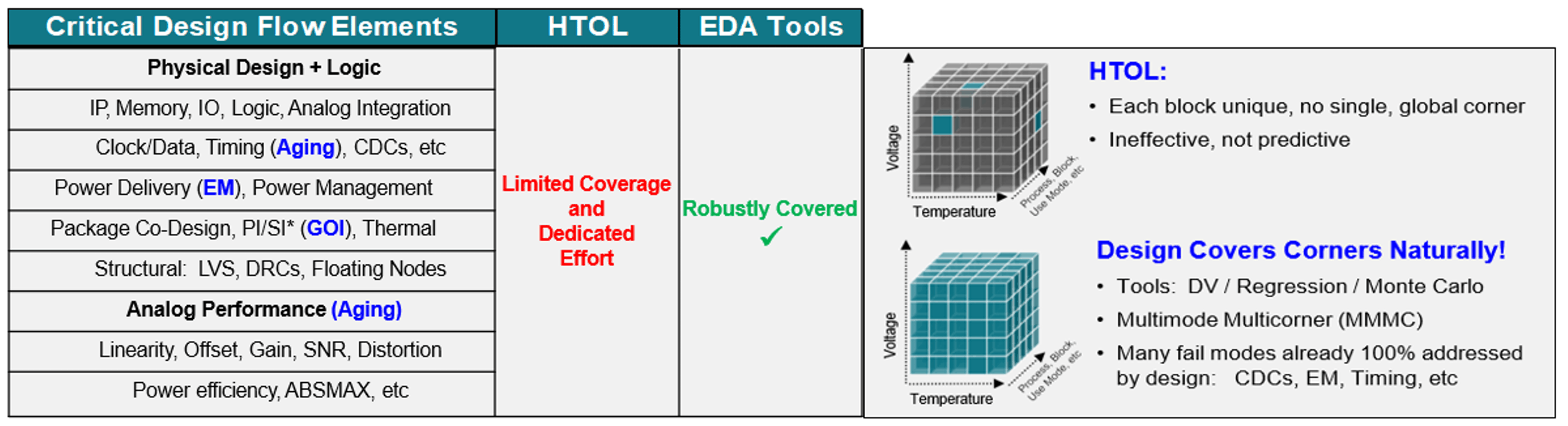

The focus of HTOL coverage is generally to maximize toggle coverage of nodes. With wear-out mechanisms, know where the relative weak spots are in the design, what operational modes are worst case and target stress pattern conditions to maximize worst case PVT and Frequency corners. Various local weak spots (IP across the die) can have different worst corners. It is very difficult with typical ATPG and BIST patterns applied in HTOL to accelerate all the worst-case functional conditions on targeted circuits. Figure 6 further expands on Figure 3 and summarizes critical aspects of the SoC design flow with a comparison of effectiveness of HTOL coverage vs. EDA tools as Design Verification paths. Applicable reliability failure mechanisms are noted.

Figure 4-1 Efficacy of HTOL vs. EDA Tools in Design Verification of Critical Design Flow Elements

For a more detailed explanation of the mathematics of HTOL-based product reliability estimates and the shortcomings, see Appendix A. Additionally, the mathematical framework for Electro-migration reliability is described in Appendix B.