SPRADJ1A June 2024 – August 2024 TMS320F280021 , TMS320F280023 , TMS320F280023C , TMS320F280025 , TMS320F280025C , TMS320F280033 , TMS320F280034 , TMS320F280037 , TMS320F280037C , TMS320F280039 , TMS320F280039C , TMS320F280041 , TMS320F280041C , TMS320F280045 , TMS320F280049 , TMS320F280049C , TMS320F28075 , TMS320F28076 , TMS320F28374D , TMS320F28374S , TMS320F28375D , TMS320F28375S , TMS320F28376D , TMS320F28376S , TMS320F28377D , TMS320F28377S , TMS320F28378D , TMS320F28378S , TMS320F28379D , TMS320F28379S , TMS320F28P550SJ , TMS320F28P650DH , TMS320F28P650DK , TMS320F28P650SH , TMS320F28P650SK

3.3 CLB Configurations

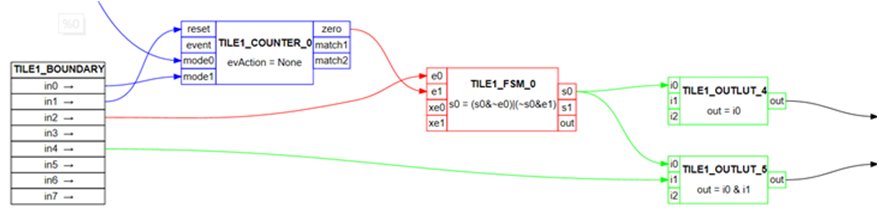

CLB is a peripheral on C2000 MCUs consisting of a number of look-up tables (LUTs), finite-state machines (FSMs) and counters which can be configured to perform complex logic operations. The LUT submodule can be used to implement simple combinatorial logic such as inverting a signal or ANDing multiple signals together. The FSM submodule can be used to implement state-based logic, such as an SR latch. The counter submodule features a 32-bit count register and can be used to perform operations such as counting the number of cycles a signal is high as well as dividing a clock signal. Interconnecting these submodules together can enable countless functions in a variety of applications. Each CLB tile contains a high-level controller (HLC) which can be triggered by signals within the CLB to perform set instructions. These instructions can include adding registers, subtracting registers, moving data between registers in the CLB, signaling interrupts to the CPU, and sending and receiving data from the CPU.

In the HHC LLC design, 2 CLB tiles are required. As for the synchronous rectification (SR) control, the challenge is to define the on time for SR PWM using normal EPWM configurations in advance, since the comparator event decides the turn-off timing of the primary-side PWM. Thus, CLB is leveraged to simplify the SR control for HHC LLC. For more details, please refer to Hardware-Based Synchronous Rectification Control with CLB.

For the primary side PWM configurations, CLB is used to make sure the identical pulse width of the high side and low side PWM signals (EPWM1A and EPWM1B). As shown in Figure 3-3, CLB is used to generated the AQ module output signal for EPWM1B, based on EPWM1A’s AQ module output signal. EPWM1A’s AQ module output signal is used to control the counter direction of CLB counter, which can start to count down after EPWM1A clears low. The natural way is to generate the symmetry counter signal. Then, by leveraging the falling edge of EPWM1A and the counter = 0 events, the expected signal for the EPWM1B can be generated by FSM.

Figure 3-3 CLB Logic for Primary Side

PWM

Figure 3-3 CLB Logic for Primary Side

PWMAs indicated in Table 3-1, it is possible to use FSM0_S0 to override the AQ module output of EPWM1B, by assigning FSM0_S0 to Output 5 of the CLB1 module, directly with the CLB multiplexer output enable register CLB_OUT_EN.

| CLB Output | CLB OUTLUT | CLB1Destination | CLB2Destination | CLB3Destination | CLB4Destination |

|---|---|---|---|---|---|

| 0 | OUTLUT0 | EPWM1A | EPWM2A | EPWM3A | EPWM4A |

| 1 | OUTLUT1 | EPWM1A_OE | EPWM2A_OE | EPWM3A_OE | EPWM4A_OE |

| 2 | OUTLUT2 | EPWM1B | EPWM2B | EPWM3B | EPWM4B |

| 3 | OUTLUT3 | EPWM1B_OE | EPWM2B_OE | EPWM3B_OE | EPWM4B_OE |

| 4 | OUTLUT4 | EPWM1A_AQ | EPWM2A_AQ | EPWM3A_AQ | EPWM4A_AQ |

| 5 | OUTLUT5 | EPWM1B_AQ | EPWM2B_AQ | EPWM3B_AQ | EPWM4B_AQ |

| 6 | OUTLUT6 | EPWM1A_DB | EPWM2A_DB | EPWM3A_DB | EPWM4A_DB |

| 7 | OUTLUT7 | EPWM1B_DB | EPWM2B_DB | EPWM3B_DB | EPWM4B_DB |

Note that to add the rising edge delay to the EPWM1B final output signal, the FSM output generated by CLB is inverted first, then the falling edge delay can be enabled within the DB module.

In addition, the requirement is to generate the synchronization event for EPWM1 module at the falling edge of EPWM1B, which can be achieved by routing FSM_S0 output to the CLB output (Output 4), and then through EPWM X-BAR to configure the synchronization scheme.

A completed CLB configuration block diagram is shown in Figure 3-4.

Figure 3-4 CLB Configuration

Diagram

Figure 3-4 CLB Configuration

Diagram