SPRUIR8B april 2020 – july 2023

- 1

- CLB Tool

- Trademarks

- 1Introduction

- 2Getting Started

- 3Using the CLB Tool

-

4Examples

- 4.1

Foundational Examples

- 4.1.1 CLB Empty Project

- 4.1.2 Example 3 – PWM Generation

- 4.1.3 Example 7 – State Machine

- 4.1.4 Example 13 – PUSH-PULL Interface

- 4.1.5 Example 14 – Multi-Tile

- 4.1.6 Example 15 – Tile to Tile Delay

- 4.1.7 Example 16 - Glue Logic

- 4.1.8 Exampe 18 - AOC

- 4.1.9 Example 19 - AOC Release Control

- 4.1.10 Example 20 - CLB XBARs

- 4.2

Getting Started Examples

- 4.2.1 Example 1 – Combinatorial Logic

- 4.2.2 Example 2 – GPIO Input Filter

- 4.2.3 Example 4 – PWM Protection

- 4.2.4 Example 5 – Event Window

- 4.2.5 Example 6 – Signal Generation and Check

- 4.2.6 Example 8 – External AND Gate

- 4.2.7 Example 9 – Timer

- 4.2.8 Example 10 – Timer With Two States

- 4.2.9 Example 11 – Interrupt Tag

- 4.2.10 Example 12 – Output Intersect

- 4.2.11 Example 17 – One-Shot PWM Generation

- 4.2.12 Example 21 - Clock Prescaler and NMI

- 4.2.13 Example 22 - Serializer

- 4.2.14 Example 23 - LFSR

- 4.2.15 Example 24 - Lock Output Mask

- 4.2.16 Example 25 - Input Pipeline Mode

- 4.2.17 Example 26 - Clocking Pipeline Mode

- 4.3 Expert Examples

- 4.1

Foundational Examples

- 5Enabling CLB Tool in Existing DriverLib Projects

- 6Frequently Asked Questions (FAQs)

- 7Revision History

3.5.3 Running the Simulation

Once the CLB configuration and input stimuli have been defined, the user can compile the project. The full steps for generating the "CLB.vcd" are outlined below.

- Enable the "Generate CLB Simulation File" check-box in the "Global Parameters" drop-down at the top of the Tile Design module.

- Build the project to verify there are no errors with the Tile Design settings

- From the file explorer or command line, execute the "clb_simulation" file. This file is located wherever the generated SysConfig files are saved. For CCS, this is the syscfg directory within the build configuration directory of the project (i.e. "CPU1_RAM/syscfg")

- Open the "simulation" directory (located one level up from the directory where "clb_simulation" is executed)

- Double-click on the "CLB.vcd" file

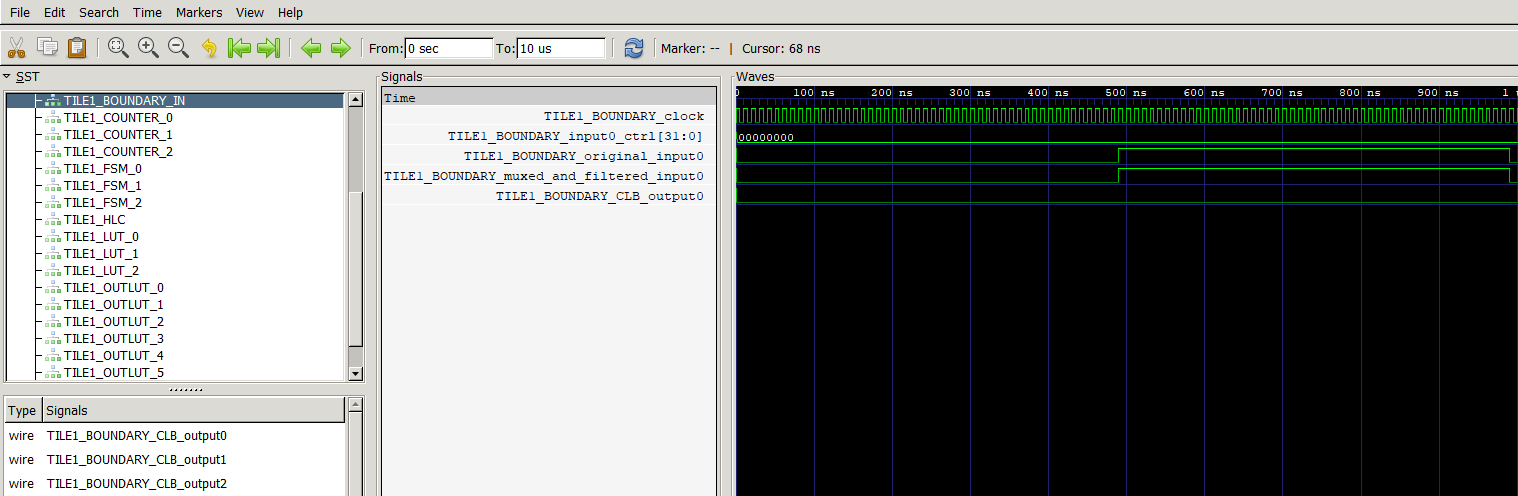

Assuming that the configuration of the waveform viewer has been completed, double-clicking on the "CLB.vcd" file should open the viewer and allow the waveforms to be inspected. Figure 3-20 shows the GTKwave viewer set up to display a sample of input waveforms. For information on how to add and view signals, see the viewer documentation.

Figure 3-20 CLB Simulation Example

Figure 3-20 CLB Simulation ExampleIf the simulated waveforms do not match expectation, modify the configuration in the .syscfg file and repeat the simulation.