SPRUIW7A October 2020 – February 2022

- Trademarks

- 1Introduction

- 2J7200 EVM Overview

- 3EVM User Setup/Configuration

-

4J7200 EVM Hardware Architecture

- 4.1 J7200 EVM Hardware Top Level Diagram

- 4.2 J7200 EVM Interface Mapping

- 4.3 I2C Address Mapping

- 4.4 GPIO Mapping

- 4.5 Power Supply

- 4.6 Reset

- 4.7 Clock

- 4.8 Memory Interfaces

- 4.9 MCU Ethernet Interface

- 4.10 QSGMII Ethernet Interface

- 4.11 PCIe Interface

- 4.12 USB Interface

- 4.13 Audio Interface

- 4.14 CAN Interface

- 4.15 FPD Interface (Audio Deserializer)

- 4.16 I3C Interface

- 4.17 ADC Interface

- 4.18 RTC Interface

- 4.19 Apple Authentication Header

- 4.20 JTAG Emulation

- 4.21 EVM Expansion Connectors

- 4.22 ENET Expansion Connector

- 5Functional Safety

- 6Revision History

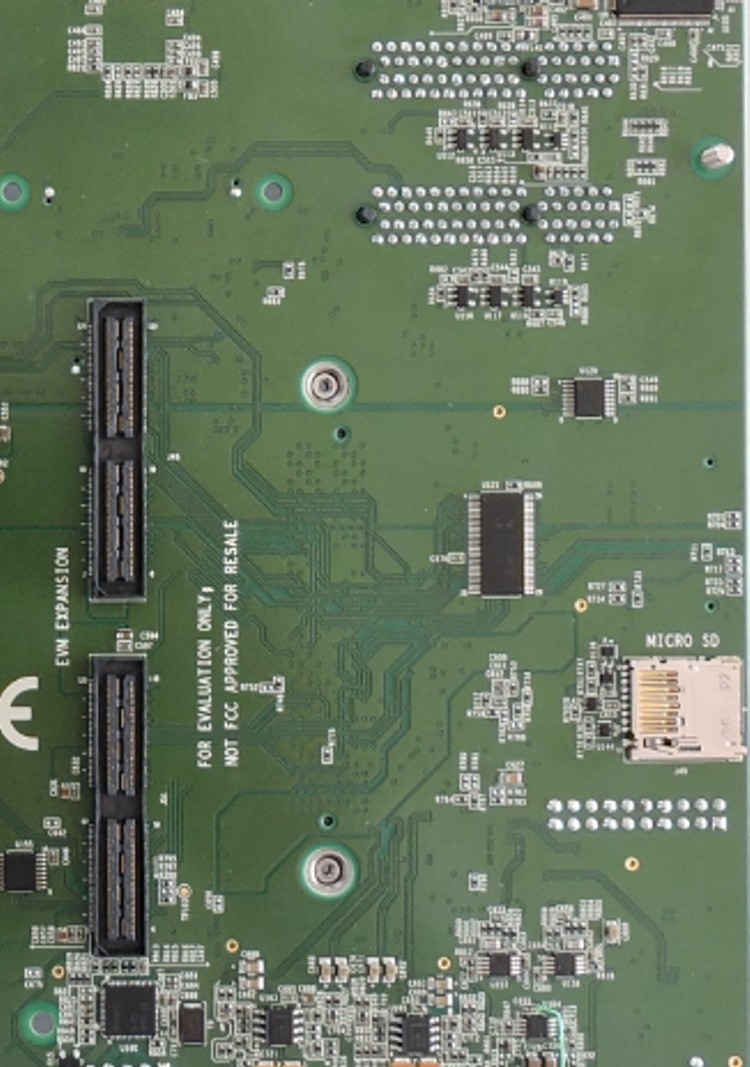

4.21 EVM Expansion Connectors

The Common processor board includes an Expansion connector of QSH-060-01-L-D-A-K with 5 mm mating height allowing multiple expansion boards (Infotainment or GESI Expansion) to be stacked below the processor board.

The GESI Expansion board can be plugged into EVM expansion connectors (J46 and J51).

Infotainment Expansion board is not supported in J7200 EVM.

Figure 4-40 Expansion Board Interface

Connectors

Figure 4-40 Expansion Board Interface

ConnectorsThe EVM Expansion connectors pinouts are shown in Table 4-28 and Table 4-29.

Table 4-28 EVM Expansion Connector J46

Pinout

| EVM Expansion Connector Interface J46 | |||

|---|---|---|---|

| Pin No. | Signal | Pin No | Signal |

| 1 | DGND | 2 | VCC_12V0 |

| 3 | DGND | 4 | VCC_12V0 |

| 5 | DGND | 6 | VCC_12V0 |

| 7 | MCASP1_AXR3/PRG0_RGMII2_RXC | 8 | VOUT0_DATA15/PRG1_RGMII2_TX_CTL |

| 9 | PRG0_RGMII2_RD3 | 10 | VOUT0_DATA14/PRG1_RGMII2_TD3 |

| 11 | MCASP1_AXR2/PRG0_RGMII2_RX_CTL | 12 | VOUT0_HSYNC/PRG1_RGMII2_TXC |

| 13 | MCASP1_AXR0/PRG0_RGMII2_RD0 | 14 | VOUT0_DATA11/PRG1_RGMII2_TD0 |

| 15 | MCASP1_AXR1/PRG0_RGMII2_RD1 | 16 | VOUT0_DATA13/PRG1_RGMII2_TD2 |

| 17 | PRG0_RGMII2_RD2 | 18 | VOUT0_DATA12/PRG1_RGMII2_TD1 |

| 19 | DGND | 20 | DGND |

| 21 | VOUT0_EXTPCLKIN/MCAN6_TX | 22 | VPFE0_DATA6/MCAN5_TX |

| 23 | VOUT0_DATA5/MCAN6_RX | 24 | VPFE0_DATA7/MCAN5_RX |

| 25 | VOUT0_DATA7/MCAN7_TX | 26 | AUDIO_EXT_REFCLK1/MCAN4_TX |

| 27 | VOUT0_DATA8/MCAN7_RX | 28 | VOUT0_DATA22/MCAN4_RX |

| 29 | VOUT0_DATA9/PRG1_UART0_RXD | 30 | PRG1_UART0_RTS# |

| 31 | VOUT0_DATA10/PRG1_UART0_TXD | 32 | VOUT0_DATA23/SPI6_CS1(PROFI_UART3_CTSn) |

| 33 | VOUT0_VSYNC/SPI6_D0 | 34 | VOUT0_DE/SPI6_CLK |

| 35 | NC | 36 | VOUT0_PCLK/SPI6_D1 |

| 37 | DGND | 38 | DGND |

| 39 | VOUT0_DATA0/PRG1_RGMII2_RD0 | 40 | VOUT0_DATA19/PRG1_RGMII1_TD3 |

| 41 | VOUT0_DATA2/PRG1_RGMII2_RD2 | 42 | VOUT0_DATA16/PRG1_RGMII1_TD0 |

| 43 | VOUT0_DATA1/PRG1_RGMII2_RD1 | 44 | VOUT0_DATA20/PRG1_RGMII1_TX_CTL |

| 45 | VOUT0_DATA3/PRG1_RGMII2_RD3 | 46 | VOUT0_DATA18/PRG1_RGMII1_TD2 |

| 47 | VOUT0_DATA4/PRG1_RGMII2_RX_CTL | 48 | VOUT0_DATA21/PRG1_RGMII1_TXC |

| 49 | VOUT0_DATA6/PRG1_RGMII2_RXC | 50 | VOUT0_DATA17/PRG1_RGMII1_TD1 |

| 51 | DGND | 52 | DGND |

| 53 | MCASP0_AXR5/MCAN9_TX | 54 | VPFE0_DATA12/PRG1_MDIO0_MDC |

| 55 | MCASP0_AXR6/MCAN9_RX | 56 | VPFE0_DATA11/PRG1_MDIO0_MDIO |

| 57 | MCASP0_ACLKX/SPI3_CS1 | 58 | SPI3_CS0 (MCAN10_TX) |

| 59 | MCASP0_AFSX/SPI3_CS2 | 60 | MCASP1_AFSX/MCAN11_RX (MCAN10_RX) |

| 61 | McASP0_AXR3 (PROFI_UART_SEL) | 62 | NC |

| 63 | WKUP_I2C0_SDA | 64 | SOC_PORZ_OUT |

| 65 | WKUP_I2C0_SCL | 66 | PRG0_PWM0_TZ_OUT (PD: GPIO_PRG1_RGMII_RST) |

| 67 | DGND | 68 | DGND |

| 69 | MCASP0_AXR0/PRG0_RGMII1_RD0 | 70 | MCASP0_AXR8/PRG0_RGMII1_TD1 |

| 71 | MCASP0_AXR2/PRG0_RGMII1_RX_CTL | 72 | MCASP0_AXR7/PRG0_RGMII1_TD0 |

| 73 | MCASP0_AXR4/PRG0_RGMII1_RXC | 74 | MCASP0_AXR11/PRG0_RGMII1_TX_CTL |

| 75 | PRG0_RGMII1_RD2 | 76 | MCASP0_AXR10/PRG0_RGMII1_TD3 |

| 77 | MCASP0_AXR1/PRG0_RGMII1_RD1 | 78 | MCASP0_AXR9/PRG0_RGMII1_TD2 |

| 79 | PRG0_RGMII1_RD3 | 80 | MCASP0_AXR12/PRG0_RGMII1_TXC |

| 81 | DGND | 82 | DGND |

| 83 | MCASP1_AXR8/PRG0_RGMII2_TD1 | 84 | MCASP6_ACLKX/PRG1_RGMII1_RD0 |

| 85 | MCASP1_AXR7/PRG0_RGMII2_TD0 | 86 | MCASP6_AFSR/PRG1_RGMII1_RXC |

| 87 | GPIO0_79/PRG0_RGMII2_TXC | 88 | MCASP6_AFSX/PRG1_RGMII1_RD1 |

| 89 | PRG0_RGMII2_TD2 | 90 | PRG1_RGMII1_RD3 |

| 91 | PRG0_RGMII2_TX_CTL | 92 | MCASP6_ACLKR/PRG1_RGMII1_RX_CTL |

| 93 | MCASP2_AXR0/PRG0_RGMII2_TD3 | 94 | MCASP6_AXR0/PRG1_RGMII1_RD2 |

| 95 | DGND | 96 | DGND |

| 97 | MDIO0_MDC | 98 | PRG0_MDIO0_MDC/I2C5_SDA |

| 99 | MDIO0_MDIO | 100 | PRG0_MDIO0_MDIO/I2C5_SCL |

| 101 | SPI3_D0 | 102 | MCASP0_AXR13/PRG0_PWM0_B2 (CAN_STB) |

| 103 | SPI3_D1 | 104 | NC |

| 105 | SPI3_CLK | 106 | RGMII_REFCLK |

| 107 | DGND | 108 | DGND |

| 109 | I2C0_SCL | 110 | MCASP1_ACLKX (GPIO_LIN_EN) |

| 111 | I2C0_SDA | 112 | SOC_I2C2_SCL |

| 113 | I2C1_SCL | 114 | SOC_I2C2_SDA |

| 115 | I2C1_SDA | 116 | NC |

| 117 | NC | 118 | EXP_RSTz |

| 119 | DGND | 120 | DGND |

Table 4-29 EVM Expansion Connector J51

Pinout

| EVM Expansion Connector Interface J51 | |||

|---|---|---|---|

| Pin no. | Signal | Pin no. | Signal |

| 1 | DGND | 2 | EXP_3V3 |

| 3 | DGND | 4 | EXP_3V3 |

| 5 | DGND | 6 | EXP_3V3 |

| 7 | MCASP1_AXR5/UART8_RXD | 8 | I2C3_SCL (I2C1_SCL) |

| 9 | MCASP1_AXR6/UART8_TXD | 10 | I2C3_SDA (I2C1_SDA) |

| 11 | EQEP0_A | 12 | EQEP0_I |

| 13 | EQEP0_B | 14 | EQEP0_S |

| 15 | GPIO1_23/UART9_RXD (GPIO_RGMII2_INT#) | 16 | EXP_CODEC_SCKI |

| 17 | GPIO1_24/UART9_TXD | 18 | NC |

| 19 | EXP_EEPROM_A0 | 20 | INFO_CAM_VIO_SEL |

| 21 | EXP_EEPROM_A1 | 22 | EXP_REFCLK |

| 23 | EXP_EEPROM_A2 | 24 | NC |

| 25 | BOARDID_EEPROM_WP | 26 | PRG1_IEP0_EDIO_OUTVALID |

| 27 | GPIO0_6 | 28 | PERIPH_RSTz |

| 29 | GPIO0_61 (GPIO_RGMII2_RST) | 30 | RESETSTATz |

| 31 | UB926_GPIO2 | 32 | EXP_MUX1 |

| 33 | UB926_GPIO3 | 34 | EXP_MUX2 |

| 35 | NC | 36 | EXP_MUX3 |

| 37 | NC | 38 | NC |

| 39 | DGND | 40 | DGND |

| 41 | GPMC0_A1 | 42 | GPMC0_A22 |

| 43 | GPMC0_A2 | 44 | GPMC0_DIR |

| 45 | GPMC0_A3 | 46 | GPMC0_A17 |

| 47 | GPMC0_A4 | 48 | GPMC0_BE1# |

| 49 | GPMC0_A5 | 50 | GPMC0_A16 |

| 51 | GPMC0_A7 | 52 | GPMC0_A21 |

| 53 | GPMC0_A6 | 54 | GPMC0_A15 |

| 55 | GPMC0_A9 | 56 | GPMC0_A20 |

| 57 | GPMC0_A11 | 58 | GPMC0_A14 |

| 59 | GPMC0_A8 | 60 | GPMC0_A18 |

| 61 | GPMC0_A10 | 62 | GPMC0_A19 |

| 63 | GPMC0_A12 | 64 | GPMC0_A13 |

| 65 | NC | 66 | NC |

| 67 | DGND | 68 | DGND |

| 69 | RESERVED_NET5 | 70 | NC |

| 71 | NC | 72 | NC |

| 73 | RESERVED_NET13 | 74 | NC |

| 75 | NC | 76 | NC |

| 77 | DGND | 78 | VSYS_5V0 |

| 79 | DGND | 80 | VSYS_5V0 |

| 81 | DGND | 82 | VSYS_5V0 |

| 83 | MCU_ADC1_AIN0 | 84 | RESERVED_NET1 (LIN2_UART_RXD) |

| 85 | MCU_ADC1_AIN1 | 86 | RESERVED_NET2 (LIN2_UART_TXD) |

| 87 | MCU_ADC1_AIN2 | 88 | RESERVED_NET4 (LIN3_UART_RXD) |

| 89 | MCU_ADC1_AIN3 | 90 | RESERVED_NET6 (LIN3_UART_TXD) |

| 91 | MCU_ADC1_AIN4 | 92 | RESERVED_NET9 (LIN4_UART_RXD) |

| 93 | MCU_ADC1_AIN5 | 94 | RESERVED_NET7 (LIN4_UART_TXD) |

| 95 | MCU_ADC1_AIN6 | 96 | RESERVED_NET3 (LIN5_UART_RXD) |

| 97 | MCU_ADC1_AIN7 | 98 | RESERVED_NET10 (LIN5_UART_TXD) |

| 99 | NC | 100 | VSYS_IO_3V3 |

| 101 | NC | 102 | VSYS_IO_3V3 |

| 103 | MCU_ADC_EXT_TRIGGER1 | 104 | VSYS_IO_3V3 |

| 105 | DGND | 106 | NC |

| 107 | I2C6_SCL | 108 | NC |

| 109 | I2C6_SDA | 110 | NC |

| 111 | NC | 112 | NC |

| 113 | USB1_DN4_PE | 114 | VSYS_IO_1V8 |

| 115 | USB1_DN4_D_N | 116 | VSYS_IO_1V8 |

| 117 | USB1_DN4_D_P | 118 | VSYS_IO_1V8 |

| 119 | DGND | 120 | DGND |