SPRUIW7A October 2020 – February 2022

- Trademarks

- 1Introduction

- 2J7200 EVM Overview

- 3EVM User Setup/Configuration

-

4J7200 EVM Hardware Architecture

- 4.1 J7200 EVM Hardware Top Level Diagram

- 4.2 J7200 EVM Interface Mapping

- 4.3 I2C Address Mapping

- 4.4 GPIO Mapping

- 4.5 Power Supply

- 4.6 Reset

- 4.7 Clock

- 4.8 Memory Interfaces

- 4.9 MCU Ethernet Interface

- 4.10 QSGMII Ethernet Interface

- 4.11 PCIe Interface

- 4.12 USB Interface

- 4.13 Audio Interface

- 4.14 CAN Interface

- 4.15 FPD Interface (Audio Deserializer)

- 4.16 I3C Interface

- 4.17 ADC Interface

- 4.18 RTC Interface

- 4.19 Apple Authentication Header

- 4.20 JTAG Emulation

- 4.21 EVM Expansion Connectors

- 4.22 ENET Expansion Connector

- 5Functional Safety

- 6Revision History

4.15 FPD Interface (Audio Deserializer)

CP Board supports TI ‘s FPD Link III De-serializer IC Mfr. Part# DS90UB926QSQE for recover the audio signals from Tuner interface using HSD connector Mfr. Part# D4S20G-400A5-C. The de-serializer will recover up to eight digital audio channels plus I2C channel across digital link.

This audio signal is connected to McASP1 port of J7200 SoC through 1:3 DEMUX (SN74CBT16214CDGGR). The channel selection is supported by both GPIO expander and EVM configuration DIP switch (SW3).

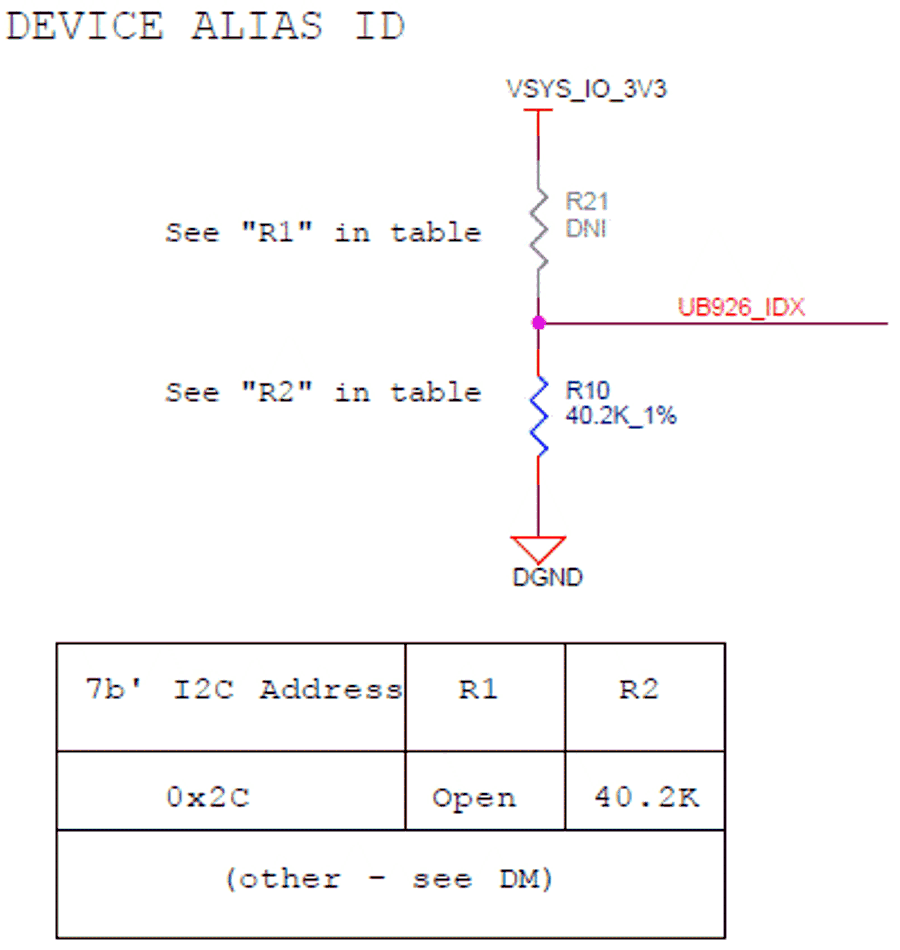

The I2C1 signals of J7200 being used for controlling of the De-serializer. A 40.2KΩ pull down is provided on ID[X] pin to set the 7‘b I2C address to 0x2C.

Figure 4-33 FPD-Link UB926 ID Setting

Circuit

Figure 4-33 FPD-Link UB926 ID Setting

CircuitPower +12V is provided to the HSD connector using a power switch TPS1H100AQPWPRQ1 to power the FPD Link-III Tuner expansion board. The power switch is controlled by a GPIO expander signal (UB926_PWR_SW_CNTRL).

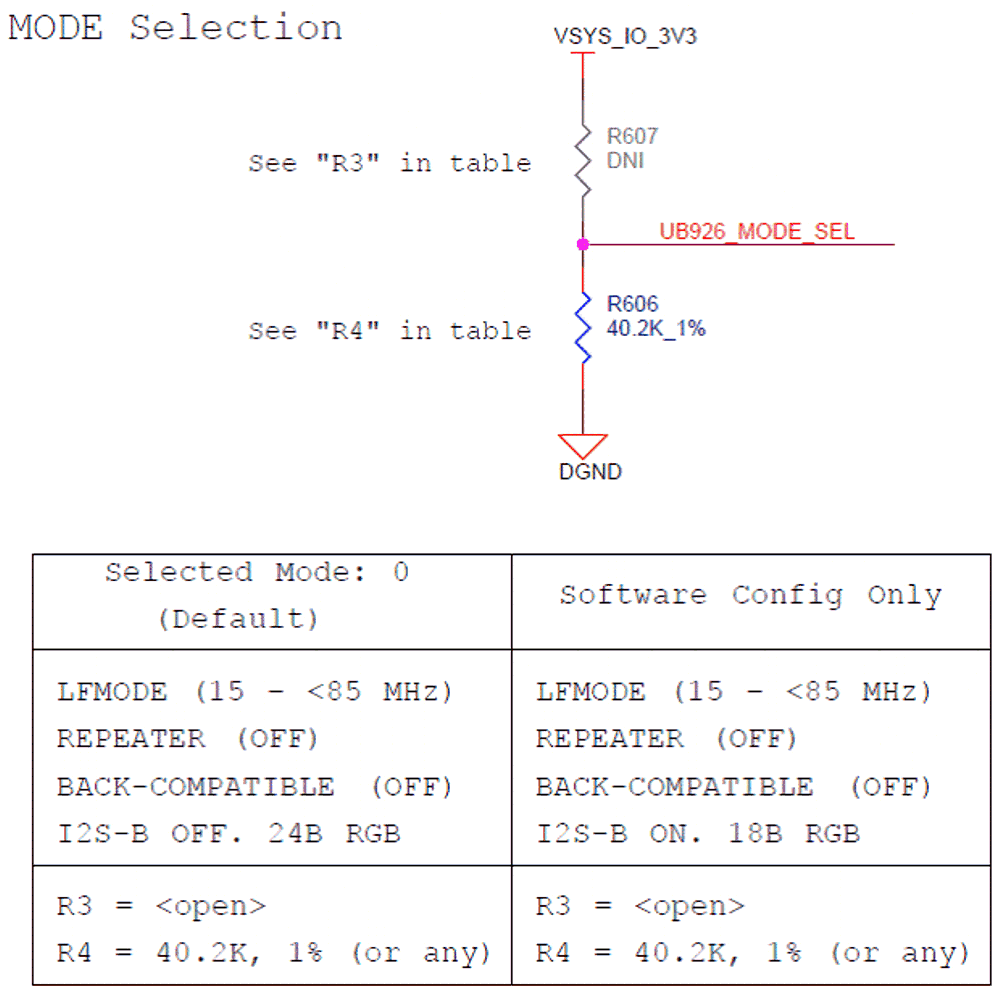

The mode selection for the de-serializer is shown in Figure 4-34.

Figure 4-34 FPD-Link UB926 Mode Selection

Circuit

Figure 4-34 FPD-Link UB926 Mode Selection

CircuitThe pin out for HSD connector J1 is given in Table 4-21.

| Pin No. | Signal |

|---|---|

| 1 | GND |

| 2 | RIN_N |

| 3 | POWER (12V) |

| 4 | RIN_P |