SPRUJ73 December 2023

2.5.5.1 PSRAM

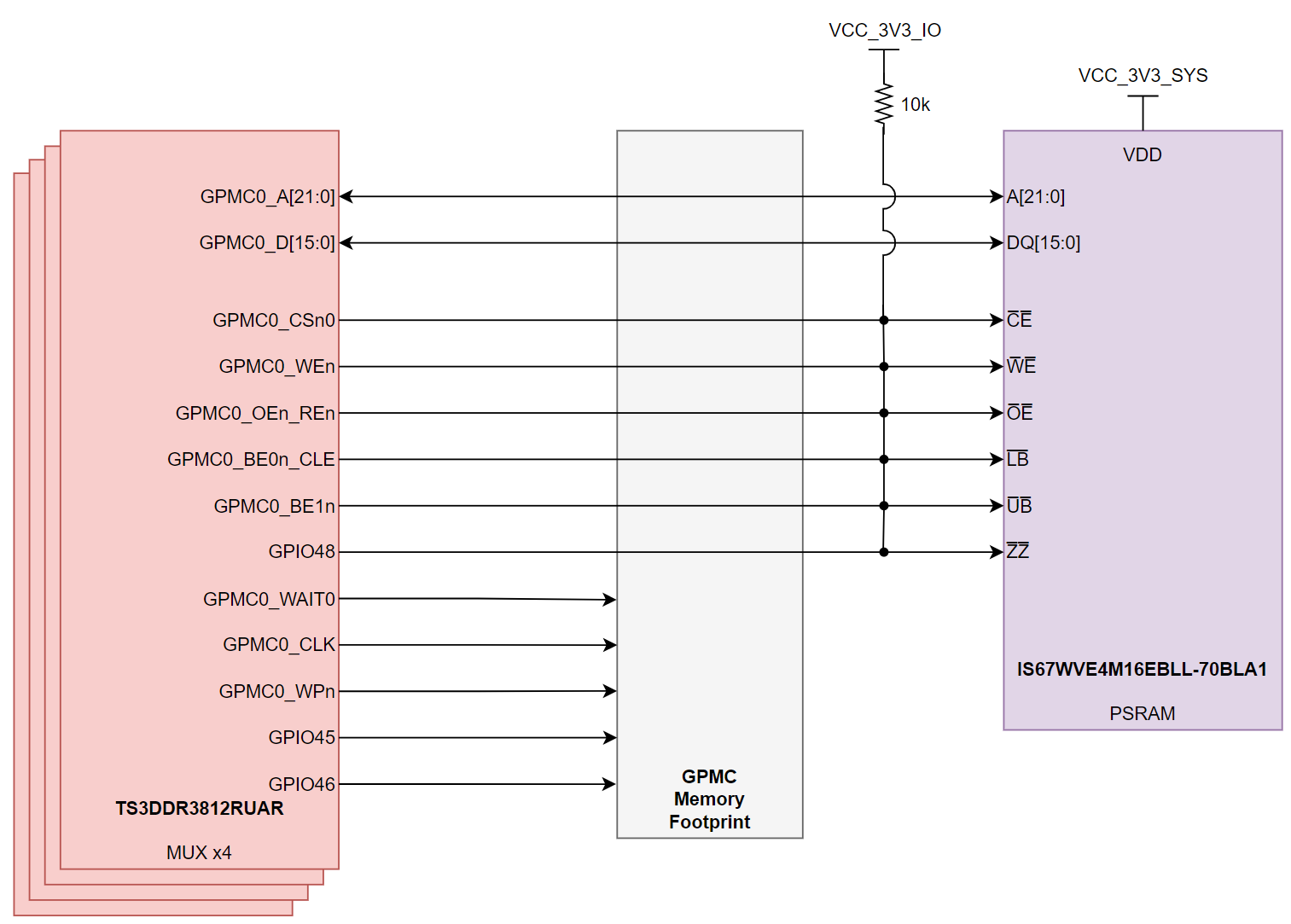

The AM263x controlCARD Docking Station has a 64Mbit PSRAM memory device (IS67WVEM16EBLL-70BLA1), which is connected to the GPMC0 interface of the AM263x SoC. The PSRAM is powered by the 3.3-V system supply.

Figure 2-12 GPMC-PSRAM Interface

Figure 2-12 GPMC-PSRAM InterfaceThe GPMC signals originating from the AM263x SoC are passed through the HSEC connector onto the Docking Station. The TRACE/GPMC multiplexing scheme sends the GPMC signals to the installed IS67WVEM16EBLL-70BLA1 64Mb PSRAM module for interfacing with an external memory device. Refer to Table 3-14 for details on the MUX scheme operation.

All select and enable signals are to be pulled high via 10 kΩ resistors to ensure functionality of the active low signals.

| AM263x Signal | IS67WVEM16EBLL-70BLA1 64Mb PSRAM Signal | ||

|---|---|---|---|

| GPMC0_A[21:0] | GPMC Address Output | A[21:0] | Address Input A[21:0] |

| GPMC0_AD[15:0] | GPMC Data Input/Output | DQ[15:0] | Data Inputs/Outputs DQ[15:0] |

| GPMC0_CSn0 | GPMC Chip Select 0 (active low) | C̅E̅ | Chip Enable/Select |

| GPMC0_WEn | GPMC Write Enable (active low) | W̅E̅ | Write Enable |

| GPMC0_OEn_REn | GPMC Output Enable (active low) or Read Enable (active low) | O̅E̅ | Output Enable |

| GPMC0_BE0n_CLE | GPMC Lower-Byte Enable (active low) or Command Latch Enable | L̅B̅ | Lower Byte Select |

| GPMC0_BE1n | GPMC Upper-Byte Enable (active low) | U̅B̅ | Upper Byte Select |

| GPMC0_WAIT0 | GPMC External Indication of Wait | N/A | N/A |

| GPMC0_WPn | GPMC Flash Write Protect (active low) | N/A | N/A |

| GPIO45 | General-Purpose IO 45 | N/A | N/A |

| GPIO46 | General-Purpose IO 46 | N/A | N/A |

| GPIO48 | General-Purpose IO 48 | Z̅Z̅ | Sleep Enable |