SPRUJ74 January 2023

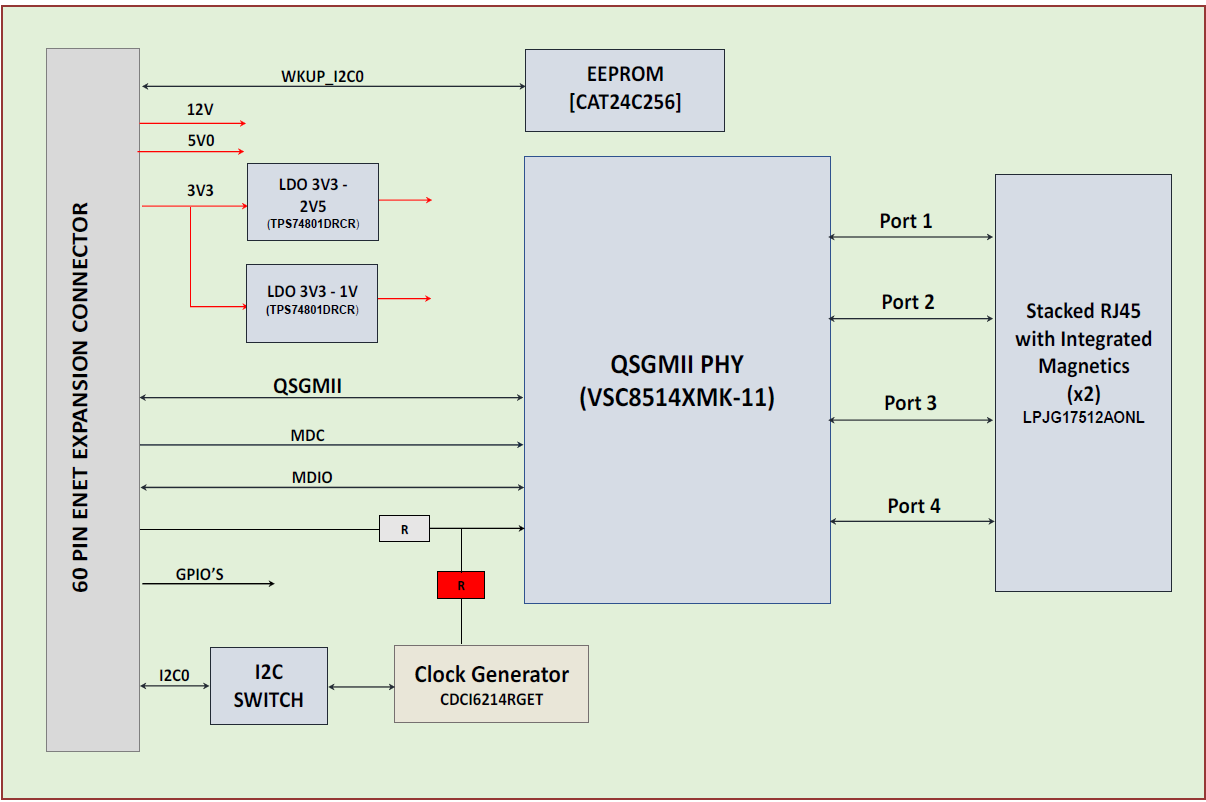

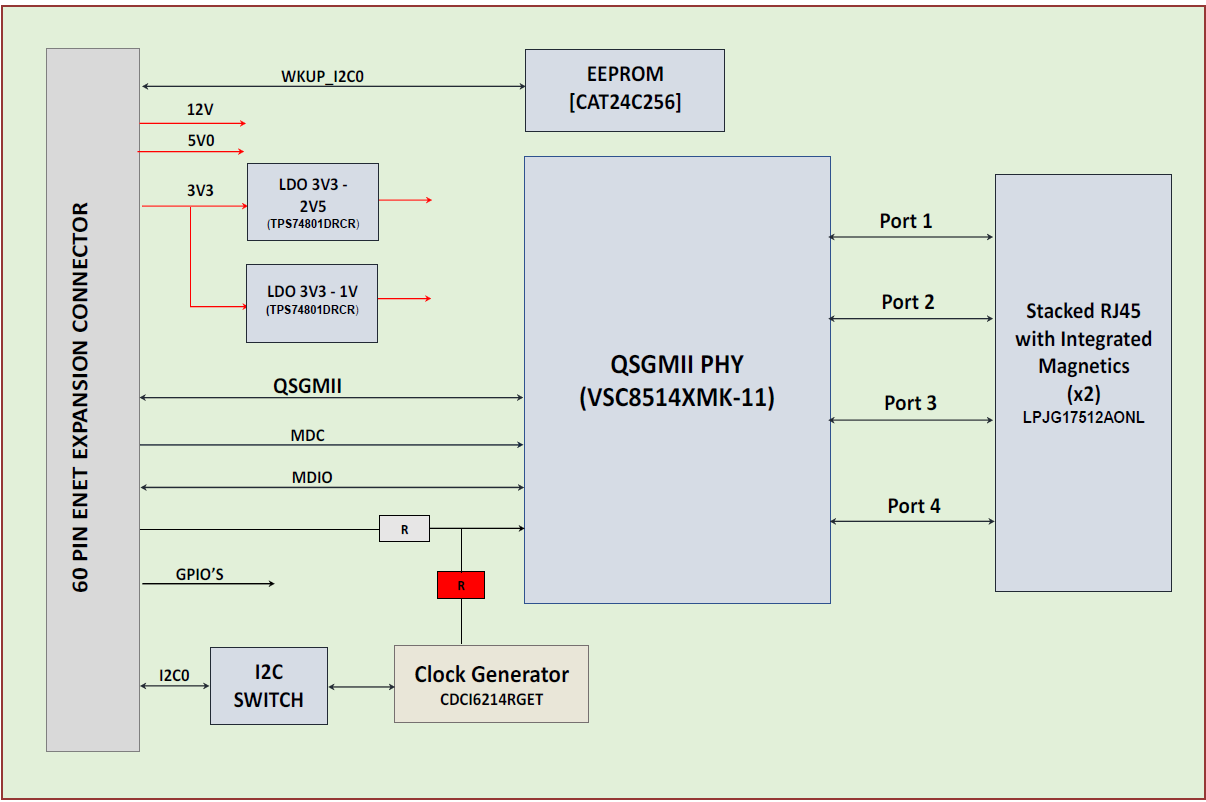

3.1 QP-ENET Expansion Board Hardware Top Level Diagram

The generic functional block diagram of the QP-ENET Expansion Board is shown below.

Figure 3-1 Functional Block Diagram of QP-ENET Expansion Board

Figure 3-1 Functional Block Diagram of QP-ENET Expansion BoardSPRUJ74 January 2023

The generic functional block diagram of the QP-ENET Expansion Board is shown below.

Figure 3-1 Functional Block Diagram of QP-ENET Expansion Board

Figure 3-1 Functional Block Diagram of QP-ENET Expansion Board