SPRUJ85 April 2024

ADVANCE INFORMATION

- 1

- Description

- Key Features

- 1LaunchPad Module Overview

-

2Hardware Description

- 3.1 Board Setup

- 3.2 Functional Block Diagram

- 3.3 GPIO Mapping

- 3.4 Reset

- 3.5 Clock

- 3.6 Memory Interface

- 3.7 Ethernet Interface

- 3.8 I2C

- 3.9 Industrial Application LEDs

- 3.10 SPI

- 3.11 UART

- 3.12 MCAN

- 3.13 FSI

- 3.14 JTAG

- 3.15 TIVA and Test Automation Header

- 3.16 LIN

- 3.17 MMC

- 3.18 ADC and DAC

- 3.19 EQEP and SDFM

- 3.20 EPWM

- 3.21 BoosterPack Headers

- 3.22 Pinmux Mapping

- 3Additional Information

- 4References

- 5Revision History

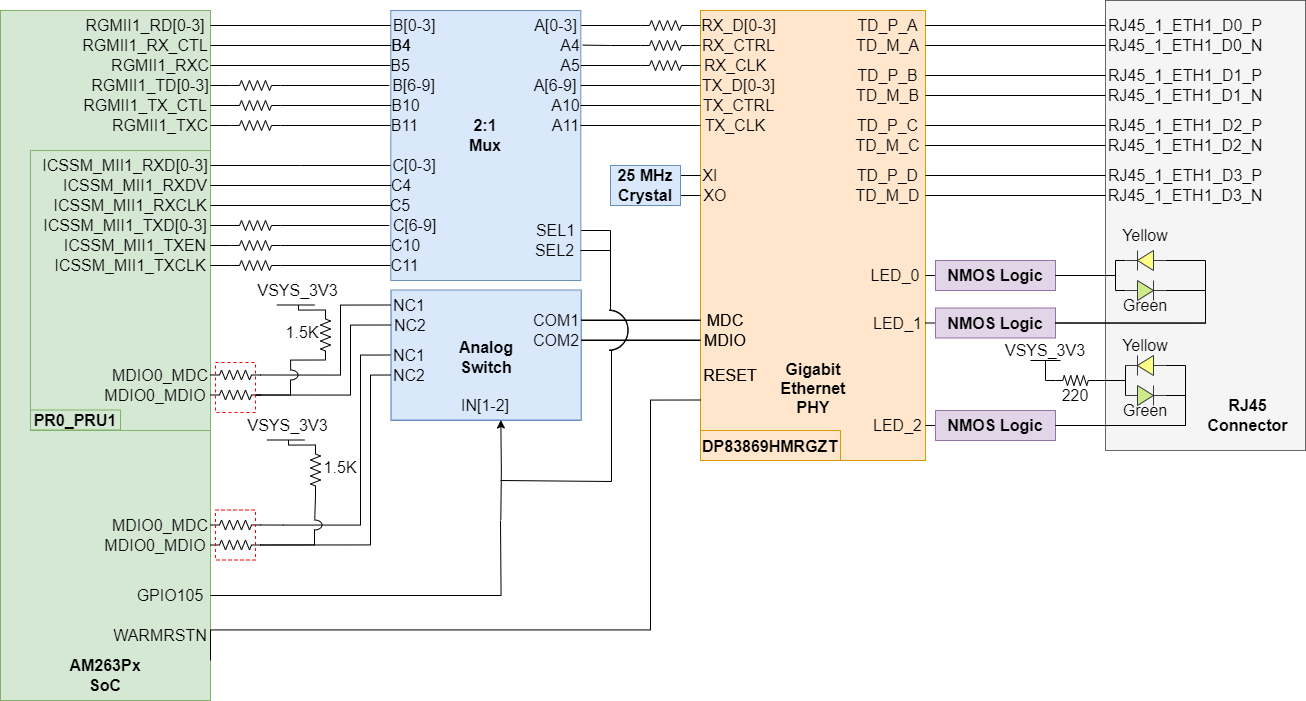

2.7.1 Ethernet PHY #1 - CPSW RGMII/ICSSM

The AM263Px LaunchPad utilizes a 48-pin Ethernet PHY (DP83869HMRGZT) connected to either CPSW RGMII or one on-die Programmable Real-time Unit and Industrial Communication Sub System (PRU-ICSS). There is a 2:1 mux that selects between the RGMII or PRU-ICSS signals. The PHY is configured to advertise 1-Gb operation. The Ethernet data signals of the PHY are terminated to an RJ45 connector. The RJ45 connector is used on the board for Ethernet 10/100/1000Mbps connectivity with integrated magnetics and LEDs for link and activity indication.

Figure 2-15 Ethernet PHY #1

Figure 2-15 Ethernet PHY #1The Ethernet PHY requires three separate power sources. VDDIO is the 3.3V, system generated supply. There are dedicated LDO's for the 1.1V and 2.5V supplies for the Ethernet PHY.

There are series termination resistors on the transmit clock and data signals located near the SoC. There are series termination resistors on the receive clock and data signals near the Ethernet PHY.

The MDIO signal from the SoC to the PHY require 1.5kΩ pullup resistors to the 3.3V system supply voltage for proper operation. There is an analog switch (TS5A23159DGSR) that selects between the CPSW MDIO/MDC and the ICSSM MDIO/MDC signals to be routed to the Ethernet PHY.

Both the 2:1 mux and analog switch are controlled by a GPIO signal that selects between CPSW RGMII and ICSSM signals.

| GPIO105 | Condition | Function of Mux |

|---|---|---|

| LOW | RGMII CPSW Selected | Port A ↔ Port B |

| HIGH | ICSSM Selected | Port A ↔ Port C |

The reset input for the Ethernet PHY is controlled by the WARMRESET AM263Px SoC output signal.

The Ethernet PHY uses many functional pins as strap option to place the device into specific modes of operation.

| Functional Pin | Default Mode | Mode in LaunchPad | Function |

|---|---|---|---|

| RX_D0 | 0 | 3 | PHY address: 0011 |

| RX_D1 | 0 | 0 | |

| JTAG_TDO/GPIO_1 | 0 | 0 | RGMII to Copper |

| RX_D3 | 0 | 0 | |

| RX_D2 | 0 | 0 | |

| LED_0 | 0 | 0 | Auto-negotiation, 1000/100/10 advertised, auto MDI-X |

| RX_ER | 0 | 0 | |

| LED_2 | 0 | 0 | |

| RX_DV | 0 | 0 | Port Mirroring Disabled |