SPRUJ85A April 2024 – August 2024

PRODUCTION DATA

- 1

- Description

- 1Key Features

- 2LaunchPad Module Overview

-

3Hardware Description

- 4.1 Board Setup

- 4.2 Functional Block Diagram

- 4.3 GPIO Mapping

- 4.4 Reset

- 4.5 Clock

- 4.6 Memory Interfaces

- 4.7 Ethernet Interface

- 4.8 I2C

- 4.9 Industrial Application LEDs

- 4.10 SPI

- 4.11 UART

- 4.12 MCAN

- 4.13 FSI

- 4.14 JTAG

- 4.15 TIVA and Test Automation Header

- 4.16 LIN

- 4.17 ADC and DAC

- 4.18 EQEP and SDFM

- 4.19 EPWM

- 4.20 BoosterPack Headers

- 4.21 Pinmux Mapping

- 4Additional Information

- 5References

- 6Revision History

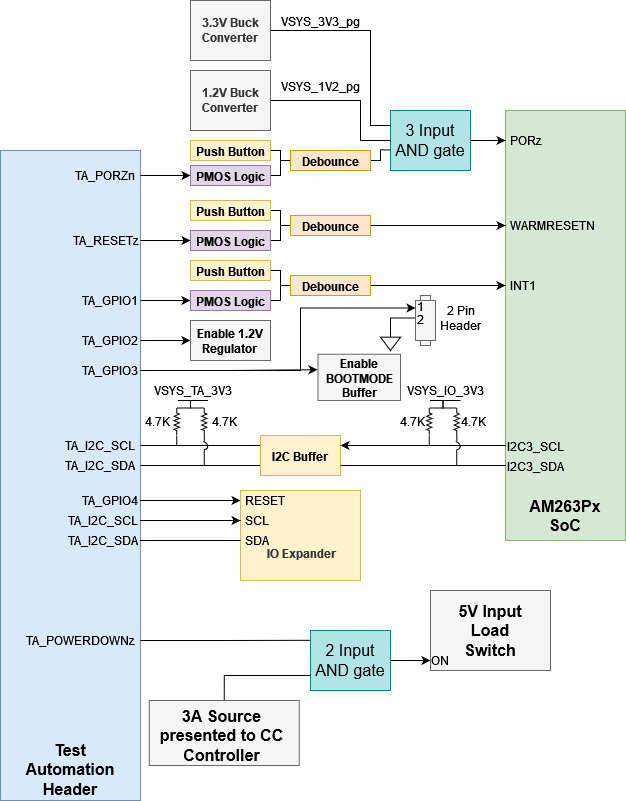

3.15 TIVA and Test Automation Header

The board supports two test automation features:

- A USB-based virtual COM port, using the TIVA Test Automation Header.

- The header allows an external controller to manipulate basic operations such as power down, PORz, warm reset, and boot mode control.

- The AM263Px SOC I2C instance is connected to the TIVA Test Automation Header - FH12A-402-0.55H.

- A 40 pin test automation header that allows an external controller to manipulate basic operations such as power down, PORz, warm reset, and boot mode control.

The Test Automation Circuit is powered by a dedicated 3.3V power supply (VSYS_TA_3V3) which is generated by a 5V to 3.3V buck regulator (TPS62177DQCR).

The AM263Px SoC I2C3 instance is connected to both the Test Automation Header and the boot mode IO expander (TCA6408ARGTR).

Figure 3-25 Test Automation Header

The following table details the Test Automation mapping.

Table 3-18 Test Automation GPIO and I2C Mapping

| Signal Name | Description | Direction |

|---|---|---|

| TA_POWERDOWNZ | When logic low, disables the 3.3V buck regulator that is used in the first stage of DC/DC conversion | Output |

| TA_PORZ | When logic low, connects the PORz signal to ground due to PMOS VGS being less than zero creating a power on reset to the MAIN domain | Output |

| TA_RESETZ | When logic low, connects the WARM RESETn signal to ground due to PMOS VGS being less than zero creating a warm reset to the MAIN domain | Output |

| TA_GPIO1 | When logic low, connects the INTn signal to ground due to PMOS VGS being less than zero creating an interrupt to SoC | Output |

| TA_GPIO3 | When logic low, disables the boot mode buffer output enable | Output |

| TA_GPIO4 | Reset signal for boot mode IO Expander | Output |

| TA_I2C_SCL | I2C Clock signal used to communicate with bootmode IO expander to change the boot modes. | Output |

| TA_I2C_SDA | I2C Data signal used to communicate with bootmode IO expander to change the boot modes. | Output |