SPRUJA1 October 2023

- 1

- Description

- Get Started

- Features

- 5

- 1Evaluation Module Overview

-

2Hardware

- 2.1 Additional Images

- 2.2 Key Features

- 2.3 Interface Mapping

- 2.4 Power ON/OFF Procedure

- 2.5 Clocking

- 2.6 Reset

- 2.7 CSI Interface

- 2.8 Audio Codec Interface

- 2.9 HDMI Display Interface

- 2.10 JTAG Interface

- 2.11 Test Automation Header

- 2.12 UART Interface

- 2.13 USB Interface

- 2.14 Memory Interfaces

- 2.15 Ethernet Interface

- 2.16 GPIO Port Expander

- 2.17 GPIO Mapping

- 2.18 OLDI Display Interface

- 2.19 Power

- 2.20 EVM User Setup/Configuration

- 2.21 Expansion Headers

- 2.22 Interrupt

- 2.23 I2C Address Mapping

- 3Hardware Design Files

- 4Compliance Information

- 5Additional Information

1.3 Specification

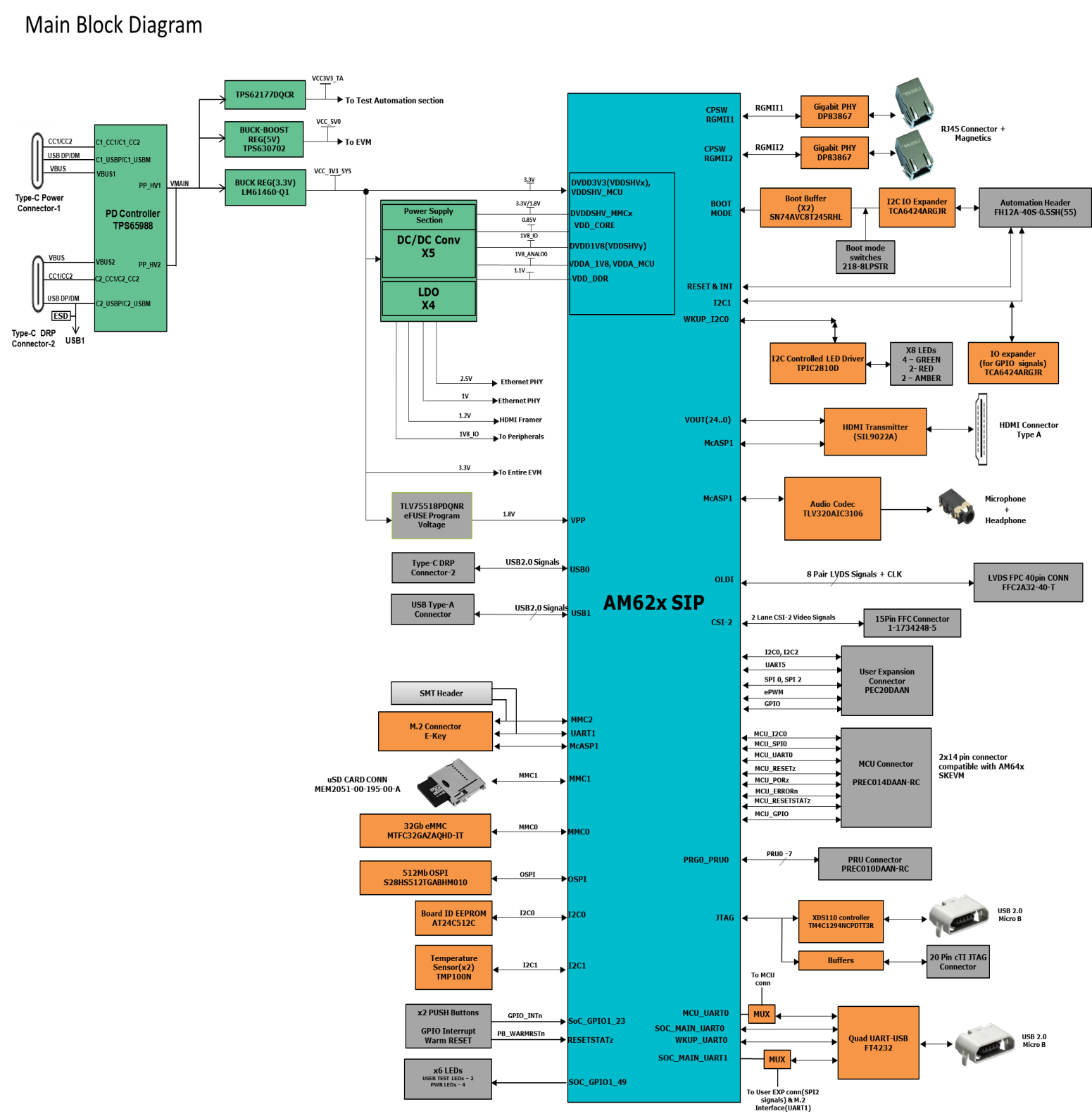

The figure below shows the functional block diagram of the AM62x SIP SK EVM.

Figure 1-1 Functional Block Diagram of

AM62x SIP SK EVM

Figure 1-1 Functional Block Diagram of

AM62x SIP SK EVM