SPRUJA3 November 2024 F29H850TU , F29H859TU-Q1 , TMS320F28374D , TMS320F28375D , TMS320F28376D , TMS320F28377D , TMS320F28378D , TMS320F28379D

- 1

- Abstract

- Trademarks

- 1Feature Differences Between F2837x, F2838x, F28P65x and F29H85x

- 2C29x Architecture

- 3PCB Design Consideration

-

4Feature Differences for System

Consideration

- 4.1

New Features in F29H85x

- 4.1.1 Analog Subsystem

- 4.1.2 Data Logger and Trace (DLT)

- 4.1.3 Single Edge Nibble Transmission (SENT)

- 4.1.4 Waveform Analyzer Diagnostic (WADI)

- 4.1.5 EPWM

- 4.1.6 Bootrom

- 4.1.7 ERAD

- 4.1.8 XBAR

- 4.1.9 Error Signaling Module (ESM)

- 4.1.10 Error Aggregator

- 4.1.11 Hardware Security Module (HSM)

- 4.1.12 Safe Interconnect End-to-End (E2E) Safing

- 4.1.13 Critical MMR Safing With Parity

- 4.1.14 LPOST

- 4.2 Communication Module Changes

- 4.3 Control Module Changes

- 4.4 Analog Module Differences

- 4.5 Power Management

- 4.6 Memory Module Changes

- 4.7 GPIO Multiplexing Changes

- 4.1

New Features in F29H85x

- 5Software Development with F29H85x

- 6References

2.1.1 Peripheral Interrupt Priority and Expansion (PIPE)

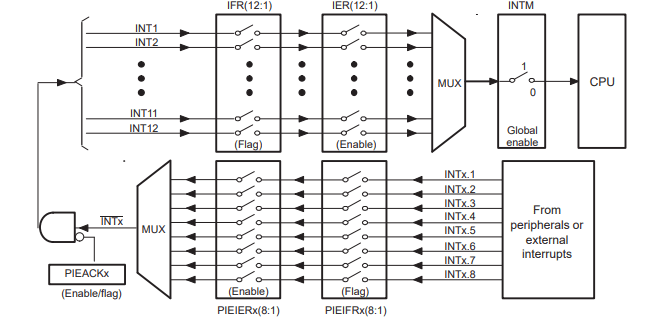

In C28x, the primary interrupt controller was the Peripheral Interrupt Expansion (PIE). In C29x, the primary interrupt controller is the Peripheral Interrupt Priority and Expansion (PIPE). The PIPE module arbitrates peripheral interrupts across the device. All asserted interrupts are arbitrated each clock cycle, with the highest priority interrupt asserted to the appropriate CPU interrupt line (NMI, RTINT, or INT). The PIPE module is responsible for providing vector addresses to the CPU for NMI, RTINT, INT and RESET. The PIPE is capable custom ordering of interrupts and hardware nesting. For more information, see the F29H85x and F29P58x Real-Time Microcontrollers Technical Reference Manual.

Figure 2-1 PIE Architecture

Figure 2-1 PIE Architecture Figure 2-2 PIPE Architecture

Figure 2-2 PIPE Architecture| Feature | C28x PIE | C29x PIPE |

|---|---|---|

| Hardware Prioritization | No (Software only) | Yes |

| Hardware Arbitration | No (Software only) | Yes |

| Hardware Nesting | No | Yes (can block using groups) |

| Peripheral Interrupt Type | 1 | 2 (RTINT/INT) |

| Stack Overflow Tracking | No | Yes |

| Peripheral Interrupt Count | 192 (on most devices) | 256 |