SSZT882 November 2017

The idea of “cycle scavenging” is built into the DNA of C2000 microcontrollers (MCUs), which enables them to minimize latency at every stage of real-time control without compromising performance.

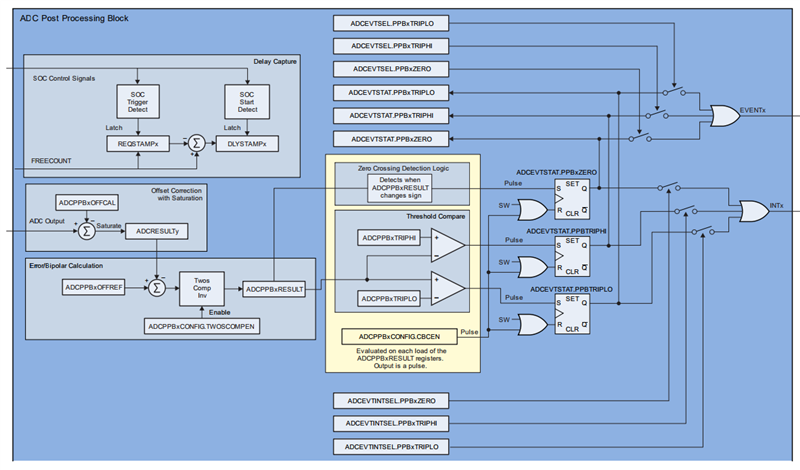

In previous installments of this series, I looked at a number of features on C2000 MCUs, including zero-wait-state analog-to-digital converter (ADC) transfers, multiport ADC reads, start-of-conversion timing and configurable ADC interrupt delays that are tailored to scavenge cycles at the sensing stage of real-time closed-loop control systems. In this installment, I’ll take a closer look at how the ADC post-processing blocks shown in Figure 1 provide a unique way of scavenging cycles from the main processors that would otherwise be required in the middle of your most time-critical loops.

Figure 1 ADC Post-processing Block

Diagram

Figure 1 ADC Post-processing Block

DiagramTraditionally, the main processors of an MCU handled sample-processing routines such as offset correction, error calculation and threshold comparisons. This took place during the processing stage of closed-loop systems. With the addition of ADC post-processing blocks on new C2000 MCUs, these routines are now performed during the sensing stage, with zero software overhead.

Offset correction

Error computation

Threshold detection

Moving on from sensing, in the next installment of this blog series I will address processing, discussing the trigonometric math unit and control law accelerator and their abilities to scavenge cycles at the processing stage of real-time control systems.

Additional Resources

- Download the “TMS320F2837xD Dual-Core Delfino™ Microcontrollers Technical Reference Manual” and “The TMS320F2837xD Architecture: Achieving a New Level of High Performance” technical brief.

- Download the “TMS320F28004x Piccolo™ Microcontrollers Technical Reference Manual.”

- Read the blog post, “Achieve unprecedented current-loop performance from an off-the-shelf MCU.”