SWRU612 December 2023 CC3300 , CC3301 , CC3301MOD , CC3351

- 1

- Abstract

- Trademarks

- 1Introduction

-

2Schematic Considerations

- 2.1 Schematic Reference Design

- 2.2 Power Supply

- 2.3 Clock Source

- 2.4 Radio Frequency (RF)

- 2.5 Digital Interfaces

- 3Layout Considerations

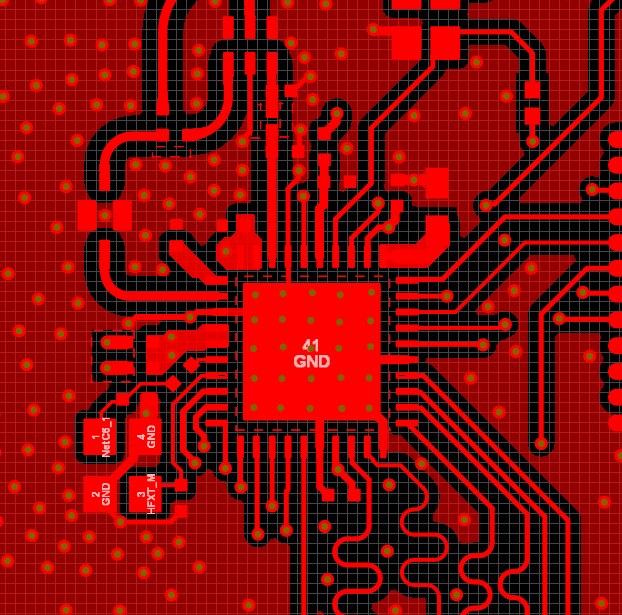

3.1.2 BP-CC3301 Design Layout

Figure 3-3 is sampled from the BP-CC3301 design files.

Figure 3-3 BP-CC3301 Layout , Top (Layer 1)

Figure 3-3 BP-CC3301 Layout , Top (Layer 1)Figure 3-4 is sampled from the BP-CC3301 design files.

Figure 3-4 BP-CC3301 Layout, Ground (Layer 2)

Figure 3-4 BP-CC3301 Layout, Ground (Layer 2)