SWRU612 December 2023 CC3300 , CC3301 , CC3301MOD , CC3351

- 1

- Abstract

- Trademarks

- 1Introduction

-

2Schematic Considerations

- 2.1 Schematic Reference Design

- 2.2 Power Supply

- 2.3 Clock Source

- 2.4 Radio Frequency (RF)

- 2.5 Digital Interfaces

- 3Layout Considerations

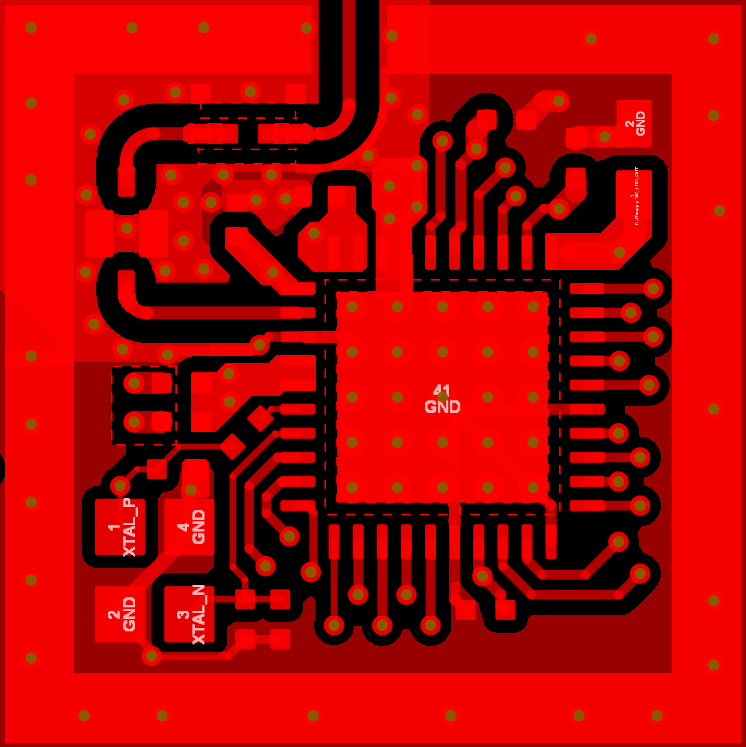

3.2 IC Thermal Pad

Underneath the IC, there should be one continuous ground plane on the top layer with 25 vias evenly distributed as shown in the Figure 3-7. This is important for thermal dissipation and optimal RF performance.

Figure 3-7 is sampled from the CC330x reference design files.

Figure 3-7 Reference Design Thermal

Pad

Figure 3-7 Reference Design Thermal

Pad