TIDT262 April 2022

- Description

- Features

- Applications

- 1Test Prerequisites

-

2Testing and

Results

- 2.1 Efficiency Graphs

- 2.2 Load Regulation

- 2.3 Line Regulation

- 2.4

Thermal Images

- 2.4.1

Further Extensive Thermal

Measurements

- 2.4.1.1

No Forced Cooling

- 2.4.1.1.1 Thermal Images 4.5 VIN and 20 AOUT

- 2.4.1.1.2 Thermal Image 5.5 VIN and 20 AOUT

- 2.4.1.1.3 Thermal Image 7 VIN and 25 AOUT

- 2.4.1.1.4 Thermal Image 9 VIN and 30 AOUT

- 2.4.1.1.5 Thermal Image 12 VIN and 30 AOUT

- 2.4.1.1.6 Thermal Image 15 VIN and 30 AOUT

- 2.4.1.1.7 Thermal Image 13.8 VIN and 30 AOUT

- 2.4.1.2 Forced Cooling

- 2.4.1.1

No Forced Cooling

- 2.4.1

Further Extensive Thermal

Measurements

- 2.5 Bode Plots

- 3Waveforms

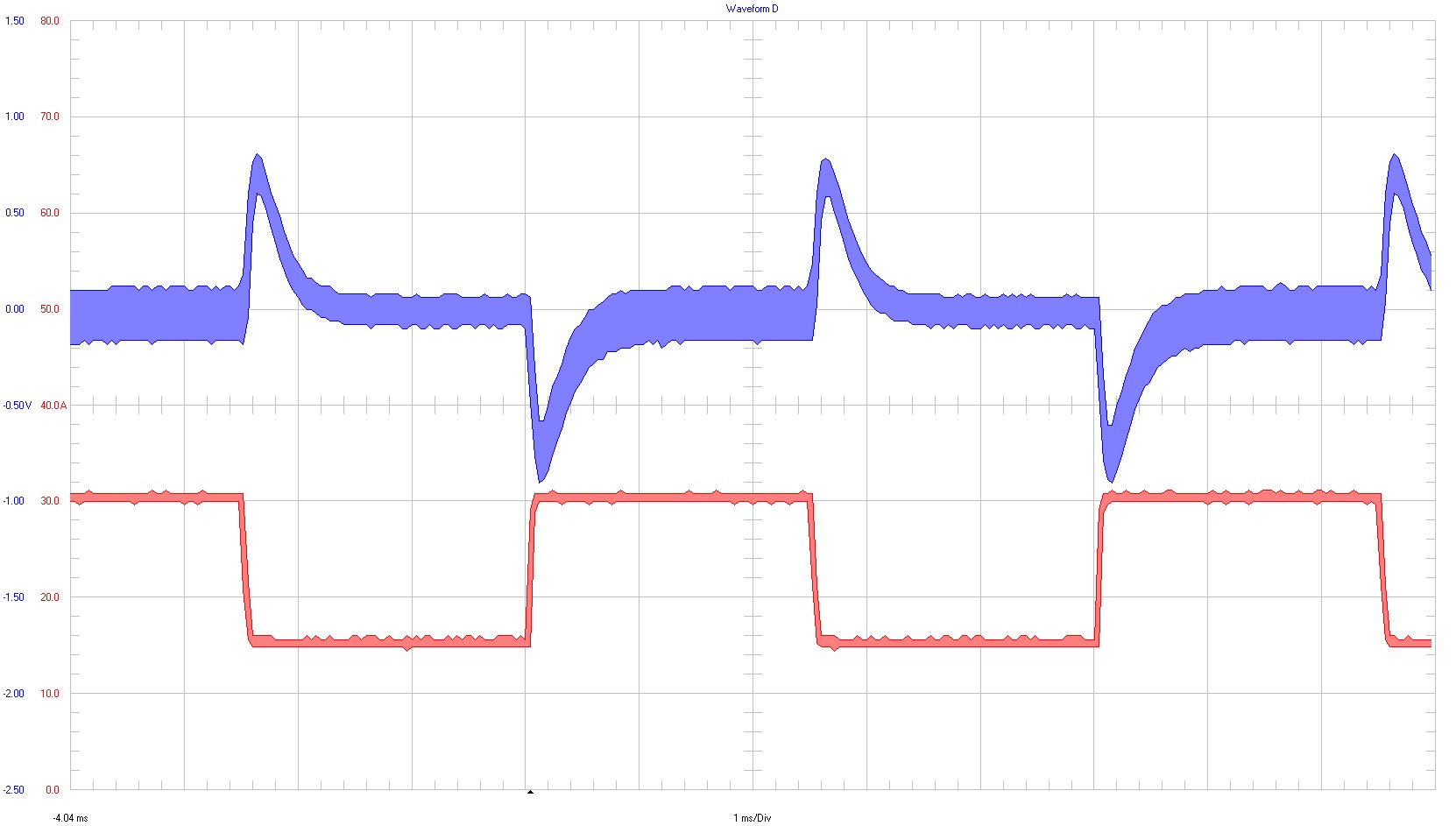

3.4.1 9-V Input Voltage

Ch1 ⇒ VOUT 0.5 V /

div

Ch2 ⇒ IOUT 10 A / div

1 ms / div

20-MHz bandwidth

Figure 3-25 Load Transient for 9-V Input

VoltageCh2 ⇒ IOUT 10 A / div

1 ms / div

20-MHz bandwidth