TIDT316 December 2022

- Description

- Features

- Applications

- 1Test Prerequisites

- 2Testing and Results

- 3Waveforms

- A Output Ripple Reduction, Output Current Capability, and Dithering Option

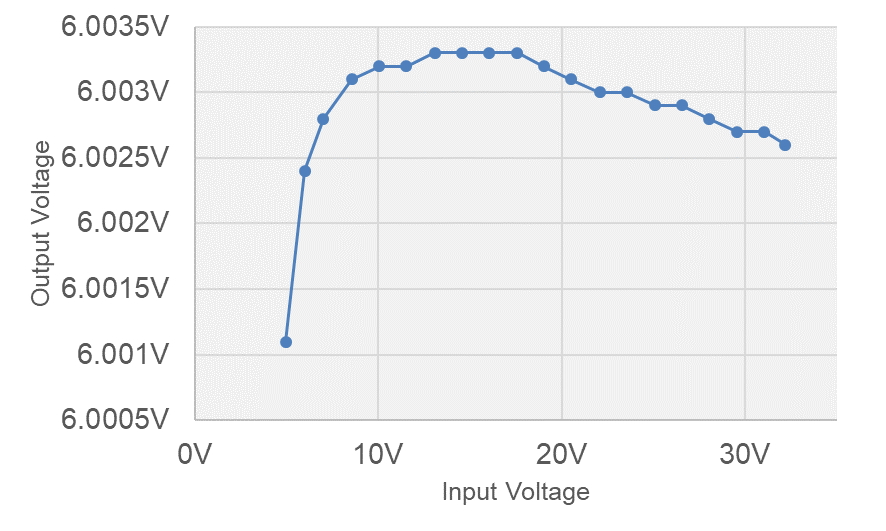

2.4 Line Regulation

Figure 2-4 Output Voltage vs Input

Voltage of Power-Stage

Figure 2-4 Output Voltage vs Input

Voltage of Power-StageThe measurement for line regulation data was gathered for efficiency and loss.

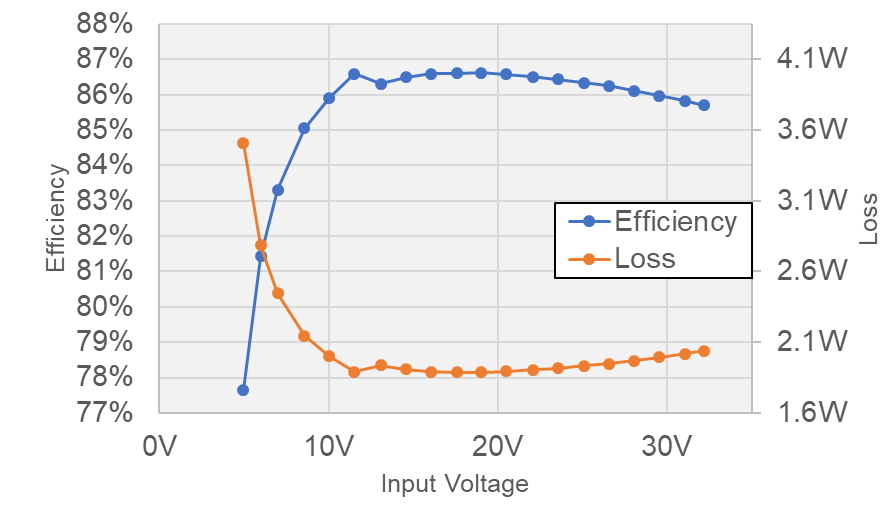

Figure 2-5 Efficiency and Loss vs Input

Voltage of Power-Stage

Figure 2-5 Efficiency and Loss vs Input

Voltage of Power-StageThe irregularity in the curves at 11.5-V to 13-V input voltage is related to the measurement range change from the input current.