TIDT316 December 2022

- Description

- Features

- Applications

- 1Test Prerequisites

- 2Testing and Results

- 3Waveforms

- A Output Ripple Reduction, Output Current Capability, and Dithering Option

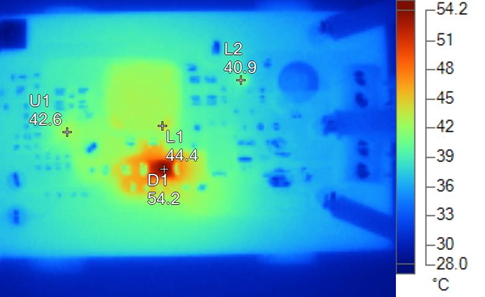

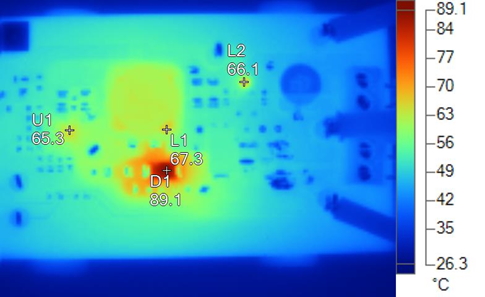

2.5.1 8-V Input Voltage

Table 2-1 Temperature Values for 8

VIN

| Name | 1 AOUT | 2 AOUT |

|---|---|---|

| D1 | 54.2°C | 89.1°C |

| L1 | 44.4°C | 67.3°C |

| L2 | 40.9°C | 66.1°C |

| U1 | 42.6°C | 65.3°C |

Table 2-2 Thermal Images for 8

VIN

| 1 AOUT | 2 AOUT |

|---|---|

|

|