John Betten

フライバック コンバータは、連続導通モード (CCM) または不連続導通モード (DCM) で動作可能です。ただし、多くの低消費電力および低電流アプリケーションでは、DCM フライバック コンバータを使用して、よりコンパクトで低コストのオプションを実現できます。このような設計を実施するためのステップバイステップの方法論を以下に示します。

DCM 動作は、次のスイッチング サイクルが始まる前に、コンバータの整流器電流が 0 まで減少することが特徴です。スイッチングの前に電流をゼロに減らすと、電界効果トランジスタ (FET) の散逸電力や整流器の損失が減少するほか、多くの場合、トランスの必要サイズも小さくなります。

これに対し、CCM 動作では、スイッチング期間の終わりまで整流器に電流が流れ続けます。CCM フライバックのフライバック設計のトレードオフと電力段の式については、Power Tips #76:『フライバック コンバータの設計上の考慮事項』と Power Tips #77: 『CCM フライバック コンバータの設計』で扱っています。CCM 動作は中電力から大電力のアプリケーションに最適ですが、DCM フライバックを使用できる低消費電力アプリケーションがある場合は、この記事をご覧ください。

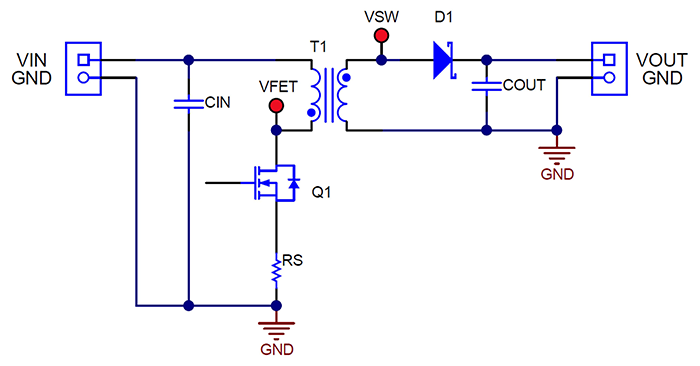

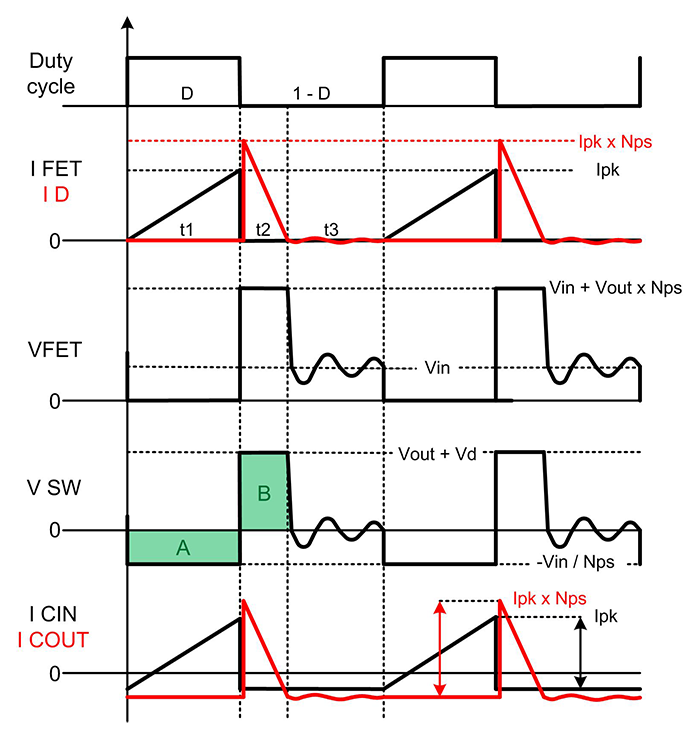

DCM または CCM モードのいずれかで動作可能な、フライバックの概略回路図を 図 1 に示します。さらに、この回路はタイミングに応じてモードを切り替えることができます。この記事で評価する DCM モードでの動作を維持するには、主要コンポーネントのスイッチング波形が 図 2 に示す特性を持っている必要があります。

デューティ サイクル D の間に FET Q1 がオンになると動作が開始します。T1 の 1 次巻線の電流は常に 0 から始まり、1 次巻線のインダクタンス、入力電圧、オン時間 t1 で決まる最大値に達します。この FET がオンになっている間は、T1 の 2 次巻線極性のためダイオード D1 が逆バイアスされ、t1 および t3 の間、すべての出力電流が出力コンデンサ COUT から強制的に供給されます。

図 1 この簡略化されたフライバック コンバータは、DCM と CCM のどちらでも動作できます

図 1 この簡略化されたフライバック コンバータは、DCM と CCM のどちらでも動作できます1-D の間に Q1 がオフになると、T1 の 2 次側電圧極性が反転し、D1 から負荷に電流が流れ COUT を再充電できるようになります。時間 t2 の間に、D1 の電流はピークからゼロまで直線的に減少します。T1 に蓄積されたエネルギーが枯渇すると、t3 の残りの期間では残留リンギングのみが発生します。このリンギングは主に T1 の磁化インダクタンスと、Q1、D1、T1 の寄生容量に起因します。これは、t3 の間の Q1 のドレイン電圧で容易に確認できます。このドレイン電圧は、VIN と反射出力電圧の合計値から VIN に戻ります。これは電流が停止した時点で、T1 が電圧をサポートできないからです(注:t3 に十分なデッドタイムがないと、CCM 動作が発生する可能性があります)。CIN および COUT の電流は Q1 および D1 の電流と同じですが、DC オフセットはありません。

図 2 の色を付けた A および B の面積は、t1 および t2 の間のトランスの電圧 (ボルト) と時間 (マイクロ秒) の積を示しており、飽和を防止するためバランスがとれている必要があります。「A」の面積は (Vin/Nps) × t1 を表し、「B」は (Vout + Vd) × t2 を表し、どちらも 2 次側を基準としています。Np/Ns はトランスの1次側と2次側の巻線比です。

図 2 DCM フライバックの主要な電圧および電流スイッチング波形には、設計者が指定する必要のあるいくつかの重要なパラメータが含まれています

図 2 DCM フライバックの主要な電圧および電流スイッチング波形には、設計者が指定する必要のあるいくつかの重要なパラメータが含まれています表 1 に、CCM と比較した DCM 動作のメリットとデメリットを示します。DCM の重要な特性の 1 つは、トランスの巻線比に関係なく、1 次側インダクタンスが小くなるとデューティ サイクルが減少することです。この特性により、設計の最大デューティ サイクルが制限されます。これは、特定のコントローラを使用する場合や、特定のオン / オフ時間の範囲に制限する場合に重要です。インダクタンスが低いと、(FET のピーク電流が大きいにもかかわらず) 必要となる平均エネルギー ストレージが小さくなり、多くの場合、CCM 設計で通常、必要となるサイズよりもトランスを小型化できます。

DCM のもう 1 つのメリットは、標準的な整流器で D1 の逆回復損失が除去されることです。これは、t2 の終わりに電流がゼロになるためです。逆回復損失は多くの場合、Q1 での散逸電力の増加として現れるため、損失を排除するとスイッチング トランジスタのストレスを低減できます。より電圧の定格が高いダイオードでは整流器の逆復帰時間が長くなるため、出力電圧が高くなると、この利点はますます重要になります。

| DCM のメリット | DCM のデメリット |

|---|---|

| CCM より低い 1 次側インダクタンス | より大きいピーク 1 次側電流 |

| 最大デューティ サイクルがインダクタンスで決まる | より大きいピーク整流電流 |

| トランスの小型化が可能 | 入力容量の増加 |

| 整流器の逆回復損失なし | 出力容量の増加 |

| FET ターンオン損失がない (または最小限) | 電磁干渉の増加の可能性 |

| 制御ループ内に右半面ゼロが存在しない | CCM よりも広いデューティ サイクル動作 |

| 低出力電力に最適 | 帯域幅変動の増加 |

開発者は、設計を開始する際に、いくつかの重要なパラメータと、基本的な電気的仕様を理解する必要があります。最初に、スイッチング周波数 (fsw)、目標とする最大動作デューティ サイクル (Dmax)、および目標効率の推定値を選択します。式 1 で、オン時間 t1 を次のように計算します。

次に、式 2 を使用して、トランスのピーク 1 次側電流 Ipk を推定します。式 2 の FET のオン電圧 (Vds_on) と電流センス抵抗電圧 (VRS) については、0.5V など、実際の設計に適した小さな電圧降下を想定します。これらの電圧降下は後で更新できます。

図 2 の A と B の面積が等しいことをもとに、式 3 で必要なトランスの巻線比 Np/Ns を計算します。

ここで、x は t3 の望ましい最小アイドル時間です (x = 0.2 から開始)。

Np/Ns を変更する場合は、Dmax を調整して、もう一度繰り返します。

次に、式 4 と 式 5 を使用して、Q1 (Vds_max) と D1 (VPIV_max) の最大「フラットトップ」電圧を計算します。

これらの成分には一般にトランスの漏れインダクタンスに起因するリンギングが発生するので、目安として、実際の値は 式 4 および 式 5 で見積もった値より 10~30% 高くなることを想定します。Vds_max が予測より大きい場合には、Dmax を小さくすると減少しますが、VPIV_max は増加します。どの電圧成分がより重要かを判断し、必要に応じて計算を繰り返します。

式 6 を使用して t1_max を計算します。これは、式 1 の値に近い必要があります。

式 7 で必要な最大 1 次側インダクタンスを計算します。

式 7 が示すよりも低いインダクタンスを選択した場合、x を増やして Dmax を下げ、Np/Ns と Lpri_max が目的の値に等しくなるまで必要に応じて計算を繰り返します。

これで 式 7 を使った Dmax の計算が可能になります。

さらに、式 9 および 式 10 を使用して、それぞれ最大 Ipk およびその最大二乗平均平方根 (RMS) の値を計算します。

選択したコントローラの電流センス入力の最小電流制限スレッショルド Vcs (式 11) に基づいて、許容される最大電流センス抵抗の値を計算します。

式 11 の Ipkmax の計算値と RS を使用して、式 2 の FET Vds とセンス抵抗 VRS の想定される電圧降下が近いことを確認します。大きく異なる場合は計算を繰り返します。

式 12 と 式 13 を使用して、RS で散逸される最大電力を計算し、Q1 の導通損失を 式 10 から計算します。

FET のスイッチング損失は一般に Vinmax で最大になるため、式 14 を使用して VIN の範囲全体にわたって Q1 のスイッチング損失を計算するのが最適です。

ここで、Qdrv は FET の総ゲート電荷量、Idrv は予測されるピーク ゲート駆動電流です。

式 15 と 式 16 で、FET の非線形 Coss 容量の充電と放電に起因する合計電力損失を計算します。式 15 の積分は、0V と実際の動作電圧 Vds の間で、実際の FET の Coss データシートの曲線によく一致している必要があります。Coss 損失は一般に、高電圧アプリケーション、または非常に小さい RDS(on) FET (Coss 値がより大きい) を使用する場合に最大になります。

FET の合計損失は、式 13、式 14、式 16 の結果を合計することで概ね見積もることができます。

式 17 は、この設計でダイオード損失の計算が大幅に簡素化されることを示しています。必ず 2 次側ピーク電流の定格を持つダイオードを選択してください。このピーク電流は一般に、IOUT よりはるかに大きくなります。

一般に、出力容量は 式 18 と 式 19 の大きい方を選択します。この場合、リップル電圧と等価直列抵抗 (式 18) または負荷過渡応答 (式 19) に基づいて容量を計算します。

ここで、∆IOUT は出力負荷電流の変化、∆VOUT は許容される出力電圧変位、fBW はコンバータの推定帯域幅です。

出力コンデンサの RMS 電流は、式 20 で計算します。

入力コンデンサのパラメータは、式 21 と 式 22 で推定します。

式 23、式 24、式 25 に、3 つの主要な波形時間間隔とそれらの関係をまとめます。

2 次側巻線を追加する必要がある場合は、式 26 で追加巻線 Ns2 を簡単に計算できます。

ここで、VOUT1 と Ns1 はレギュレートされた出力電圧です。

トランスの 1 次側 RMS 電流は、式 10 に示す FET RMS 電流と同じです。トランスの 2 次側 RMS 電流を 式 27 に示します。トランスのコアは、飽和せずに Ipk を処理できる必要があります。コア損失も考慮する必要がありますが、これはこの記事の範囲を超えています。

ここに示すステップからわかるように、DCM フライバックの設計は繰り返しのプロセスです。スイッチング周波数、インダクタンス、ターン比などの初期想定の一部は、散逸電力など、後の計算に基づいて変更される可能性があります。しかし、必要な設計パラメータを得るためには、入念に必要な設計段階を踏んでください。手間を惜しまずに行えば、最適化された DCM フライバック設計は、低消費電力、コンパクト、低コストのソリューションを実現し、パワー コンバータのニーズに対応できます。

重要なお知らせと免責事項

TI は、技術データと信頼性データ(データシートを含みます)、設計リソース(リファレンス・デザインを含みます)、アプリケーションや設計に関する各種アドバイス、Web ツール、安全性情報、その他のリソースを、欠陥が存在する可能性のある「現状のまま」提供しており、商品性および特定目的に対する適合性の黙示保証、第三者の知的財産権の非侵害保証を含むいかなる保証も、明示的または黙示的にかかわらず拒否します。

これらのリソースは、TI 製品を使用する設計の経験を積んだ開発者への提供を意図したものです。(1) お客様のアプリケーションに適した TI 製品の選定、(2) お客様のアプリケーションの設計、検証、試験、(3) お客様のアプリケーションが適用される各種規格や、その他のあらゆる安全性、セキュリティ、またはその他の要件を満たしていることを確実にする責任を、お客様のみが単独で負うものとします。上記の各種リソースは、予告なく変更される可能性があります。これらのリソースは、リソースで説明されている TI 製品を使用するアプリケーションの開発の目的でのみ、TI はその使用をお客様に許諾します。これらのリソースに関して、他の目的で複製することや掲載することは禁止されています。TI や第三者の知的財産権のライセンスが付与されている訳ではありません。お客様は、これらのリソースを自身で使用した結果発生するあらゆる申し立て、損害、費用、損失、責任について、TI およびその代理人を完全に補償するものとし、TI は一切の責任を拒否します。

TI の製品は、TI の販売条件(www.tij.co.jp/ja-jp/legal/termsofsale.html)、または ti.com やかかる TI 製品の関連資料などのいずれかを通じて提供する適用可能な条項の下で提供されています。TI がこれらのリソースを提供することは、適用されるTI の保証または他の保証の放棄の拡大や変更を意味するものではありません。IMPORTANT NOTICE

Copyright © 2024, Texas Instruments Incorporated

日本語版 日本テキサス・インスツルメンツ株式会社