-

Power Tips: Using a Simple SPICE Model to Simulate a Buck Control Loop

Power Tips: Using a Simple SPICE Model to Simulate a Buck Control Loop

John Betten

When powering up your buck converter for the first time, wouldn’t it be nice to be confident that it will be stable? This is certainly possible by using a simple simulation model and a few simple calculations to set the error amplifier and power-stage gains.

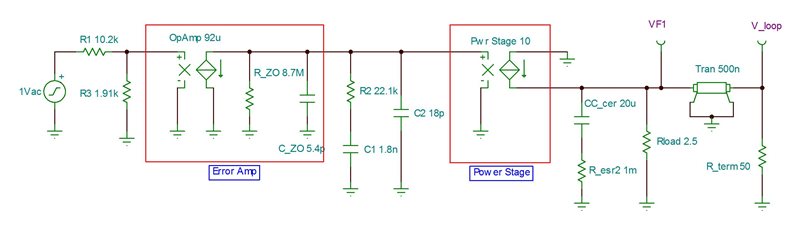

Figure 1 shows a current-mode (CM) model with the error amplifier, power-stage gain and output filter. The error amplifier looks at the output voltage, compares it to an internal reference voltage, and generates an error signal to the power stage. The power-stage gain block converts the error voltage into output current. Simple voltage-controlled current sources model both gains. Adding a lossless transmission line to the output introduces phase lag, improving accuracy at higher bandwidths (BWs).

Figure 1 CM Control-loop Model

Figure 1 CM Control-loop ModelA 1Vac perturbation is injected into the feedback and propagates to the power-stage filter output, V_loop, to measure the system’s loop gain. Making the feedback connection to the positive input of the error amplifier rather than the negative eliminates phase shift. This makes the power supply’s phase margin directly readable at V_loop.

You must determine two error-amplifier parameters: DC gain and operational-amplifier (op-amp) BW. Most controller data sheets specify both parameters. To model the op-amp’s open-loop frequency response, first calculate the output impedance (R_ZO) by dividing the open loop gain of 800V/V (or 58dB) by its transconductance of 92µA/V. This gives an output impedance of 8.7MOhms. Next, calculate the low-frequency pole to set its BW to 2.7MHz, as specified in the data sheet. A pole at 2.7MHz/800 or 3.4kHz is required. Using this pole frequency and the output impedance of 8.7MOhms results in an output capacitance of 5.4pF. Components R2, C1 and C2 provide the external compensation necessary to stabilize the power supply.

I set the power-stage block’s gain to 10A/V based on the data sheet. With CM control, the peak current follows the error signal, turning the inductor into a current source and eliminating it from the model. The output-filter component values must be accurate. They affect the filter pole and zero frequencies, which affect the converter BW and the resulting phase response. Be sure to de-rate the ceramic output capacitor’s capacitance for DC bias, which can often be far less than the stated value. An aluminum capacitor’s equivalent series resistance (ESR) can increase more than tenfold when operated cold, so be sure to verify stability using the highest expected ESR.

The transmission line introduces phase lag, which improves accuracy at higher frequencies. This phase lag is a result of propagation delay and relates to the time the converter actually takes to switch from when initially commanded. An average delay time is about one-half the switching period and introduces a 90° phase lag at one-half the switching frequency. For low-BW converters, the effect will be small. However, as the BW approaches one-half the switching frequency, the phase decreases significantly and better matches the actual phase response. Without this in the model, expect the phase-response error to increase above one-tenth the switching frequency.

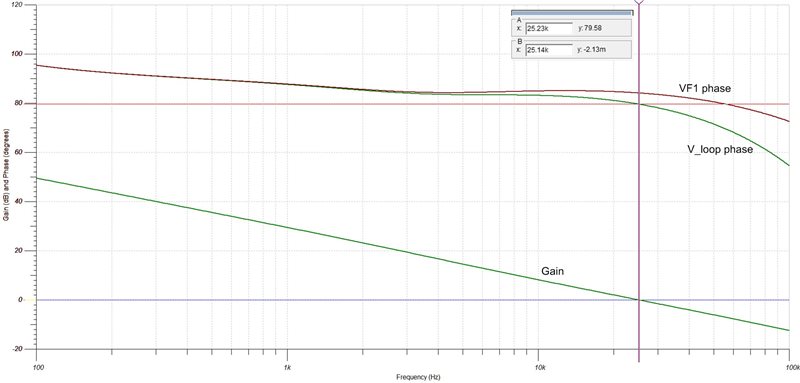

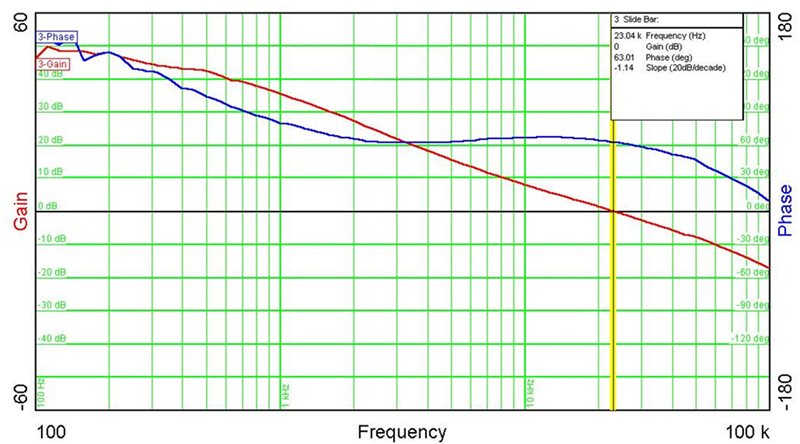

Figure 2 shows the simulated response, while Figure 3 shows the actual measurement. The transmission line decreases the phase at higher frequencies. There is good correlation between the predicted and actual data; however, some error between the two does exist. These differences are likely due to factors such as internal slope compensation and value discrepancies. Figure 2 Simulated CM Model’s Gain and

Phase Margin

Figure 2 Simulated CM Model’s Gain and

Phase Margin Figure 3 Lab Measurement Shows Good

Correlation

Figure 3 Lab Measurement Shows Good

CorrelationThis model provides a simple method to validate compensation values in CM buck converters with reasonable accuracy. The simulated results can validate stability; reduce test time; and model the effects of second stage L-C filters, long inductive leads and downstream capacitances. It is most useful when setting the initial BW lower for checkout, verifying stability and optimizing for a higher BW.

Additional Resources

- Check out TI’s Power Tips blog series on Power House.

- For more about this topic, see the Power Tips article, “Power Tips: Simulate your buck converter control loop.”

IMPORTANT NOTICE AND DISCLAIMER

TI PROVIDES TECHNICAL AND RELIABILITY DATA (INCLUDING DATASHEETS), DESIGN RESOURCES (INCLUDING REFERENCE DESIGNS), APPLICATION OR OTHER DESIGN ADVICE, WEB TOOLS, SAFETY INFORMATION, AND OTHER RESOURCES “AS IS” AND WITH ALL FAULTS, AND DISCLAIMS ALL WARRANTIES, EXPRESS AND IMPLIED, INCLUDING WITHOUT LIMITATION ANY IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE OR NON-INFRINGEMENT OF THIRD PARTY INTELLECTUAL PROPERTY RIGHTS.

These resources are intended for skilled developers designing with TI products. You are solely responsible for (1) selecting the appropriate TI products for your application, (2) designing, validating and testing your application, and (3) ensuring your application meets applicable standards, and any other safety, security, or other requirements. These resources are subject to change without notice. TI grants you permission to use these resources only for development of an application that uses the TI products described in the resource. Other reproduction and display of these resources is prohibited. No license is granted to any other TI intellectual property right or to any third party intellectual property right. TI disclaims responsibility for, and you will fully indemnify TI and its representatives against, any claims, damages, costs, losses, and liabilities arising out of your use of these resources.

TI’s products are provided subject to TI’s Terms of Sale (www.ti.com/legal/termsofsale.html) or other applicable terms available either on ti.com or provided in conjunction with such TI products. TI’s provision of these resources does not expand or otherwise alter TI’s applicable warranties or warranty disclaimers for TI products.

Mailing Address: Texas Instruments, Post Office Box 655303, Dallas, Texas 75265

Copyright © 2023, Texas Instruments Incorporated