JAJSC87B May 2016 – August 2016 REF6125 , REF6130 , REF6133 , REF6141 , REF6145 , REF6150

PRODUCTION DATA.

1 特長

- 優れた温度ドリフト係数性能

- -40℃~+125℃の範囲で8ppm/℃ (最大値)

- 非常に低ノイズ

- 総ノイズ: 47µFコンデンサで5µVRMS

- 1/fノイズ(0.1Hz~10Hz): 3µVPP/V

- ADCドライブ・バッファ内蔵

- 低い出力インピーダンス: 50mΩ未満(0~200kHz)

- ADS8881との組み合わせで最初のサンプルでも18ビットの精度

- バースト・モードのDAQシステムに対応

- 低い消費電流: 820μA

- 低いシャットダウン時電流: 1µA

- 高い初期精度: ±0.05%

- 非常に低いノイズと歪み

- 出力電流ドライブ: ±4mA

- 短絡電流をプログラム可能

- ADS88xxファミリのSAR ADCおよびADS127xxファミリの広帯域ΔΣ ADCのREFピンを駆動できることを確認済み

2 アプリケーション

- ATEテスターおよびオシロスコープ

- テストおよび計測機器

- PLC用のアナログ入力モジュール

- 医療用機器

- 高精度データ・アクイジション・システム

3 概要

REF6000ファミリの電圧リファレンスには、低出力インピーダンスのバッファが搭載されているため、ユーザーは高精度データ・コンバータのREFピンを直接駆動しながら、直線性、歪み、ノイズ性能を維持できます。ほとんどの高精度SARおよびデルタ-シグマADCでは、変換プロセス中に、バイナリ重み付けされたコンデンサをREFピン上に切り替えます。この動的な負荷をサポートするため、電圧リファレンスの出力は、低い出力インピーダンス(高い帯域幅)のバッファを経由する必要があります。REF6000ファミリのデバイスは、ADS88xxファミリのSAR ADC、ADS127xxファミリのデルタ-シグマADC、および他のD/Aコンバータ(DAC)のREFピンを駆動するのに最適ですが、他の用途にも使用できます。

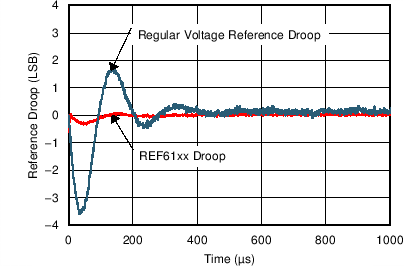

REF6000ファミリの電圧リファレンスは、ADS8881のREFピンを駆動中の最初の変換時でも出力電圧が1 LSB (18ビット)以上低下しません。この機能は、バースト・モード、イベント・トリガ、等価時間サンプリング、可変サンプリング・レートのデータ・アクイジション・システムに非常に便利です。REF6000ファミリのREF61xxバリエーションは、最大温度ドリフト係数の定格がわずか8 ppm/℃で、電圧リファレンスと低インピーダンスの出力バッファの両方の組み合わせについて、初期精度が0.05%です。REF6000ファミリの各種の温度ドリフト係数オプションについては、デバイス比較表を参照してください。

製品情報(1)

| 型番 | パッケージ | 本体サイズ(公称) |

|---|---|---|

| REF61xx | VSSOP (8) | 3.00mm×3.00mm |

- 提供されているすべてのパッケージについては、データシートの末尾にあるパッケージ・オプションについての付録を参照してください。

代表的なアプリケーション

リファレンス電圧低下の比較

(1 LSB = 19.07µV、ADS8881で1 MSPSの場合)