電源設計へのアプローチ方法 - 第 4 部

このアプリケーション・ブリーフでは、SEPIC (single-ended primary inductance converter) とゼータ・コンバータについて説明します。どちらのトポロジも、最大 25W の電力範囲の昇降圧コンバータに代わる、コスト効率の優れた代替品になる可能性があります。

SEPICs

SEPIC トポロジは、入力電圧の昇圧と降圧を行うことができます。スイッチ Q1 が導通していない場合、エネルギーが入力から出力に転送されます。図 1 に非同期 SEPIC の回路図を示します。

図 1 非同期 SEPIC の回路図

式 1 で、連続導通モード (CCM) でのデューティ・サイクルを次のように計算します。

式 2 で、MOSFET (metal-oxide semiconductor field-effect transistor) の最大ストレスを次のように計算します。

式 3 で、最大ダイオード・ストレスを次のように示します。

ここで

- VIN は入力電圧

- VOUT は出力電圧

- Vf はダイオードの順方向電圧

- VC1,ripple は、カップリング・コンデンサ全体の電圧リップル

インダクタ - コンデンサ (LC) フィルタ L1 および Ci は、SEPIC の入力を指しています。これにより、連続的な電流フローによる入力でのリップルが小さくなります。出力では、パルス出力電流があるため、リップルが大きくなります。

非同期 SEPIC は、1 つのゲート・ドライバ (2 スイッチ昇降圧コンバータの場合は 2 つ) と、(4 つではなく) 2 つの半導体部品しか必要としないため、昇降圧トポロジよりもコストが低くなります。昇降圧トポロジに対する SEPIC のもう 1 つの利点は、SEPIC の連続入力電流の結果として、両方のコンバータが降圧モードで動作しているときの電磁干渉 (EMI) の挙動が優れていることです。

SEPIC は、MOSFET Q1 をローサイドで駆動する必要があるため、昇圧コントローラを使用して簡単に構築できます。

右半面ゼロ (RHPZ) は、SEPIC の達成可能なレギュレーション帯域幅の制限要因です。最大帯域幅は RHPZ 周波数の約 1/5 です。式 4 で、SEPIC の伝達関数の単一 RHPZ 周波数の推定値を次のように計算します。

式 5 で、s について次のように解くと、RHPZ が 1 つまたは 2 つ増える結果になります。

ここで

- VOUT は出力電圧

- D はデューティ・サイクル

- IOUT は出力電流

- L1 はインダクタ L1 のインダクタンス

- L2 はインダクタ L2 のインダクタンス

- C1 はカップリング・コンデンサ C1 の容量で、s は複素周波数の変数

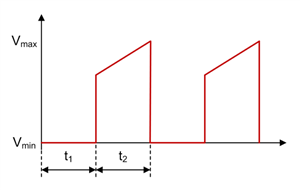

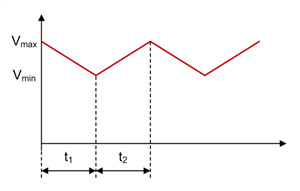

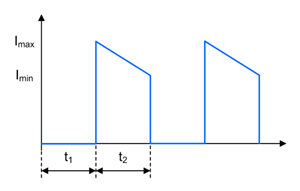

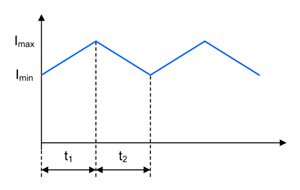

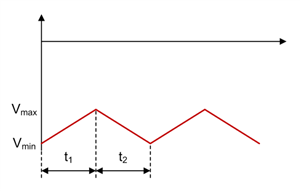

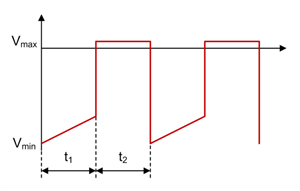

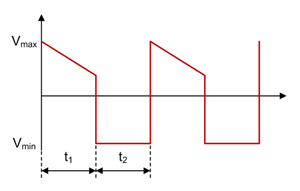

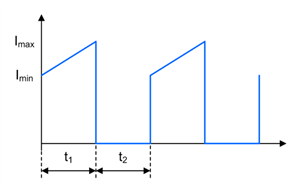

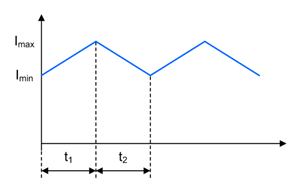

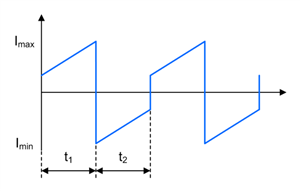

図 2 から 図 11 に、非同期 SEPIC の FET Q1、インダクタ L1、カップリング・コンデンサ C1、ダイオード D1、インダクタ L2 に対する CCM の電圧と電流の波形を示します。

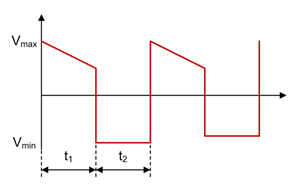

図 2 CCM での SEPIC FET Q1 電圧波形

図 4 CCM での SEPIC インダクタ L1 電圧波形

図 6 CCM での SEPIC カップリング・コンデンサ C1 電圧波形

図 8 CCM での SEPIC ダイオード D1 電圧波形

図 10 CCM での SEPIC インダクタ L2 電圧波形

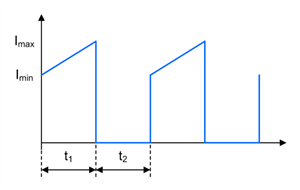

図 3 CCM での SEPIC FET Q1 電流波形

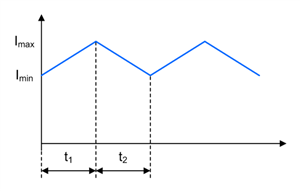

図 5 CCM での SEPIC インダクタ L1 電流波形

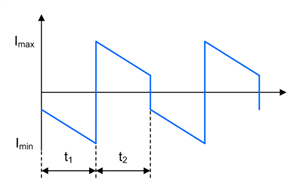

図 7 CCM での SEPIC カップリング・コンデンサ C1 電流波形

図 9 CCM での SEPIC ダイオード D1 電流波形

図 11 CCM での SEPIC インダクタ L2 電流波形

ゼータ・コンバータ

ゼータ・トポロジは、入力電圧の昇圧と降圧を行うことができます。スイッチ Q1 が導通している場合、エネルギーが入力から出力に転送されます。図 12 に非同期ゼータ・コンバータの回路図を示します。

図 12 非同期ゼータ・コンバータの回路図

式 6 で、CCM のデューティ・サイクルを次のように計算します。

式 7 で、最大 MOSFET ストレスを次のように計算します。

式 8 で、最大ダイオード・ストレスを次のように示します。

ここで

- VIN は入力電圧

- VOUT は出力電圧

- Vf はダイオードの順方向電圧

- VC1,ripple は、カップリング・コンデンサ全体の電圧リップル

ゼータ・コンバータの LC フィルタ L2 および Co は、出力を指しています。その結果、出力電流は連続的で、入力電流がパルス的であるため、入力リップルに比べて出力リップルは小さくなります。SEPIC または昇降圧コンバータが高い出力リップルに適合しない場合は、非常に敏感な負荷に対してゼータ・トポロジを使用することをお勧めします。ゼータ・トポロジには、昇降圧コンバータと比較して、コストと部品数に関して SEPIC と同じ利点があります。

ゼータ・コンバータは、降圧コントローラまたはコンバータを使用して構築できます。P チャネル MOSFET またはハイサイド MOSFET ドライバが必要です。

コントローラが出力の変化に即座に反応できるため、ゼータ・コンバータには RHPZ はありません。したがって、ゼータ・コンバータを使用する場合は、SEPIC または昇降圧コンバータを使用する場合よりも高い帯域幅を実現できますが、使用する出力容量は少なくなります。

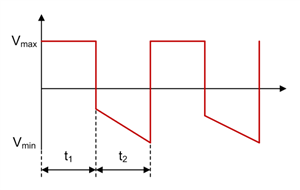

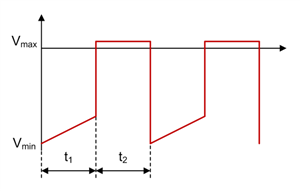

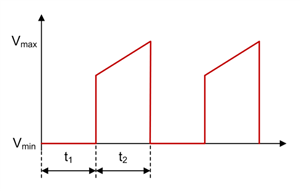

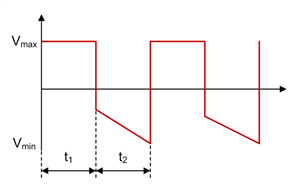

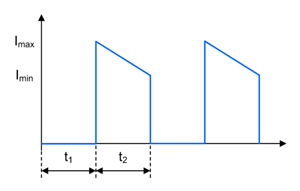

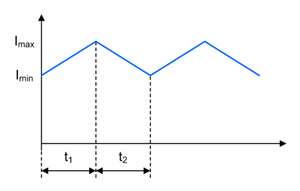

図 13 から 図 22 に、非同期ゼータ・コンバータの FET Q1、インダクタ L1、カップリング・コンデンサ C1、ダイオード D1、インダクタ L2 に対する CCM の電圧と電流の波形を示します。

図 13 CCM での ZETA FET Q1 電圧波形

図 15 CCM での ZETA インダクタ L1 電圧波形

図 17 CCM での ZETA カップリング・コンデンサ C1 電圧波形

図 19 CCM での ZETA ダイオード D1 電圧波形

図 21 CCM での ZETA インダクタ L2 電圧波形

図 14 CCM での ZETA FET Q1 電流波形

図 16 CCM での ZETA インダクタ L1 電流波形

図 18 CCM での ZETA カップリング・コンデンサ C1 電流波形

図 20 CCM での ZETA ダイオード D1 電流波形

図 22 CCM での ZETA インダクタ L2 電流波形

どちらのトポロジでも、2 つの個別インダクタではなく結合インダクタを使用することには 2 つの利点があります。1 つ目の利点は、巻線を結合することでリップルがキャンセルされるため、(2 インダクタ設計と比較して) 類似の電流リップルに必要なインダクタンスがわずか半分であることです。2 つ目の利点は、2 つのインダクタとカップリング・コンデンサに起因する伝達関数の共振を除去できることです。必要に応じて、カップリング・コンデンサ C1 と並列に抵抗コンデンサ (RC) ネットワークを接続して、この共振を減衰させます。

結合インダクタを使用する場合の欠点の 1 つは、両方のインダクタで同じインダクタンス値を使用する必要があることです。もう 1 つの制限は、一般的に電流定格です。出力電流の大きいアプリケーションでは、シングル・インダクタが必要になることがあります。

両方のトポロジを、同期整流のコンバータとして構成することができます。ただし、この方法を使用する場合は、多くのコントローラがスイッチ・ノードに接続する必要があるため、ハイサイド・ゲート・ドライブ信号を AC 結合する必要があります。どちらのトポロジにもそれぞれ 2 つのスイッチ・ノードがあるため、スイッチ・ピンで負の電圧定格違反が発生しないように注意してください。同期 SEPIC と同期ゼータ・コンバータを使用する 2 つの例は、それぞれ『12V@5A 同期 SEPIC コンバータのリファレンス・デザイン』と、『2 個のインダクタを使用する 40W 同期ゼータ・コンバータのリファレンス・デザイン』です。

その他の資料

- 以下のテキサス・インスツルメンツのトレーニング・ビデオをご覧ください。

- 以下の Analog Applications Journal の記事をお読みください。

- 『出力段の設計者』で、出力段を設計しましょう。

- 『電源トポロジ・ハンドブック』と『電源トポロジ・クイック・リファレンス・ガイド』をダウンロードしてください。

重要なお知らせと免責事項

TI は、技術データと信頼性データ(データシートを含みます)、設計リソース(リファレンス・デザインを含みます)、アプリケーションや設計に関する各種アドバイス、Web ツール、安全性情報、その他のリソースを、欠陥が存在する可能性のある「現状のまま」提供しており、商品性および特定目的に対する適合性の黙示保証、第三者の知的財産権の非侵害保証を含むいかなる保証も、明示的または黙示的にかかわらず拒否します。

これらのリソースは、TI 製品を使用する設計の経験を積んだ開発者への提供を意図したものです。(1) お客様のアプリケーションに適した TI 製品の選定、(2) お客様のアプリケーションの設計、検証、試験、(3) お客様のアプリケーションが適用される各種規格や、その他のあらゆる安全性、セキュリティ、またはその他の要件を満たしていることを確実にする責任を、お客様のみが単独で負うものとします。上記の各種リソースは、予告なく変更される可能性があります。これらのリソースは、リソースで説明されている TI 製品を使用するアプリケーションの開発の目的でのみ、TI はその使用をお客様に許諾します。これらのリソースに関して、他の目的で複製することや掲載することは禁止されています。TI や第三者の知的財産権のライセンスが付与されている訳ではありません。お客様は、これらのリソースを自身で使用した結果発生するあらゆる申し立て、損害、費用、損失、責任について、TI およびその代理人を完全に補償するものとし、TI は一切の責任を拒否します。

TI の製品は、TI の販売条件(www.tij.co.jp/ja-jp/legal/termsofsale.html)、または ti.com やかかる TI 製品の関連資料などのいずれかを通じて提供する適用可能な条項の下で提供されています。TI がこれらのリソースを提供することは、適用されるTI の保証または他の保証の放棄の拡大や変更を意味するものではありません。IMPORTANT NOTICE

Copyright © 2023, Texas Instruments Incorporated

日本語版 日本テキサス・インスツルメンツ株式会社