DLPU106A March 2021 – October 2021 DLP3021-Q1

2.3.3 LED Driver Design

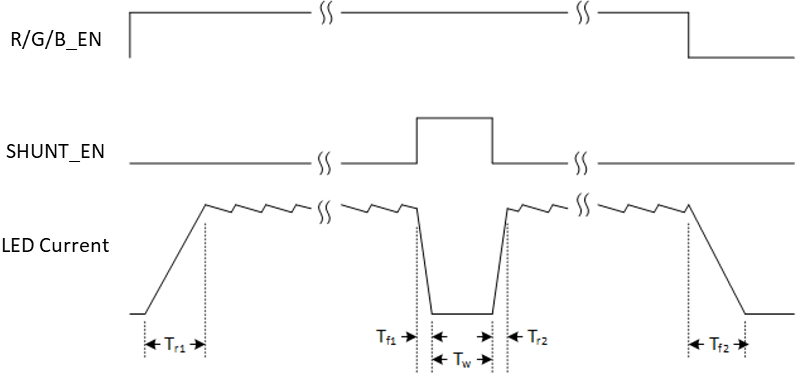

The DLP3021-Q1 chipset, used with LED illumination, includes illumination modulation based on the LM3904-Q1 P-FET buck controller for high-power LEDs. This illumination modulation turns off the light output during micromirror reset, which improves system contrast. For the system timing specifications of the DLP3021LEQ1EVM, see Figure 2-6.

Figure 2-6 LED Driver Timing Specifications

Figure 2-6 LED Driver Timing SpecificationsThe timing specifications are shown in Table 2-5.

Table 2-5 LED Driver Timing Specifications

PARAMETER | VALUE |

|---|---|

Tr1, Tf2 | < 50 μs |

Tf1, Tr2 | < 2 μs |

Tw | minimum = 1 μs |