KOKP007 April 2024

4 PSFB를 위한 클램핑 옵션

PSFB는 1차측 스위치에서 소프트 스위칭을 달성할 수 있으며, 많은 전압 링잉 없이 깨끗한 FET 드레인-소스 전압(VDS) 파형을 가질 수 있습니다. 그러나 PSFB 출력 정류기 기생 커패시턴스는 변압기 권선과 직렬로 공진하며 높은 정류기 전압 응력을 초래합니다.

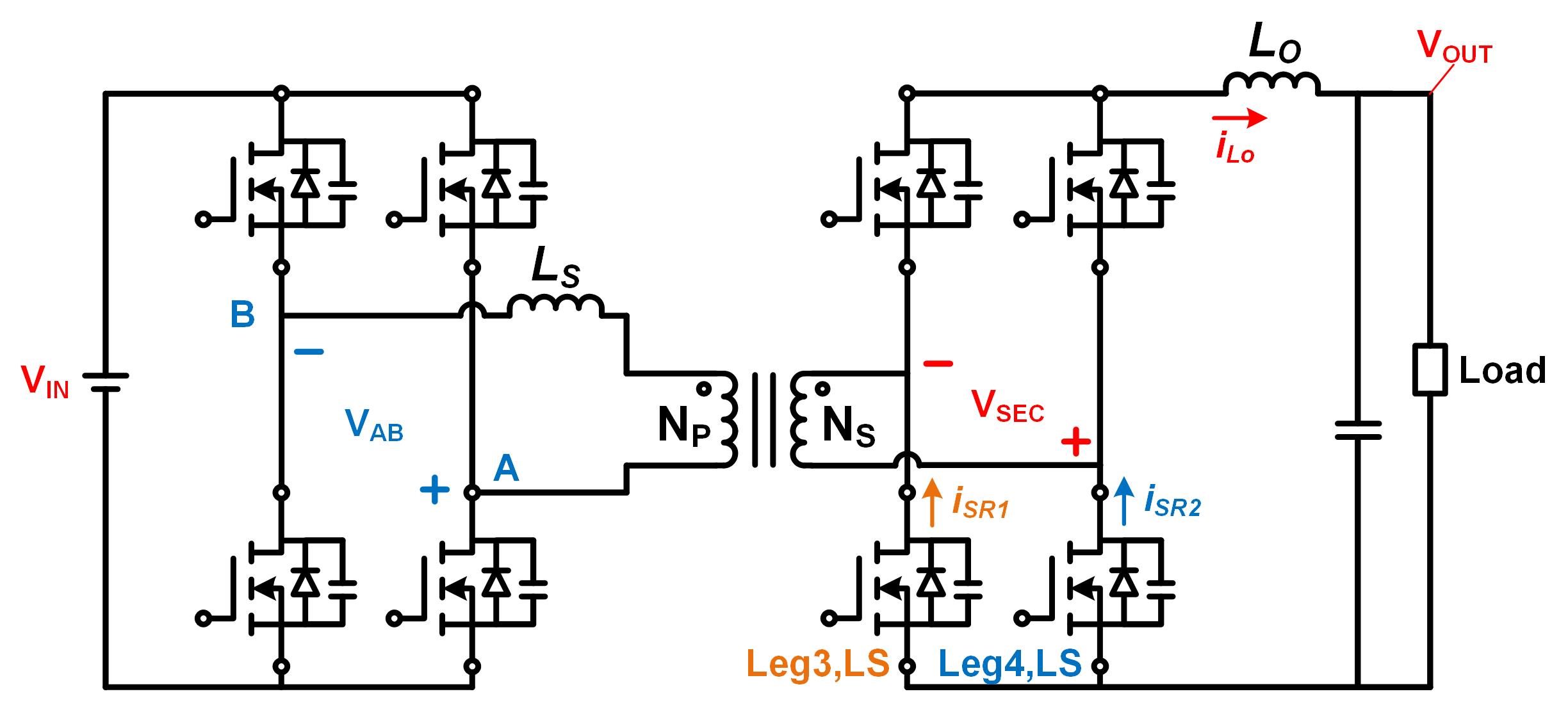

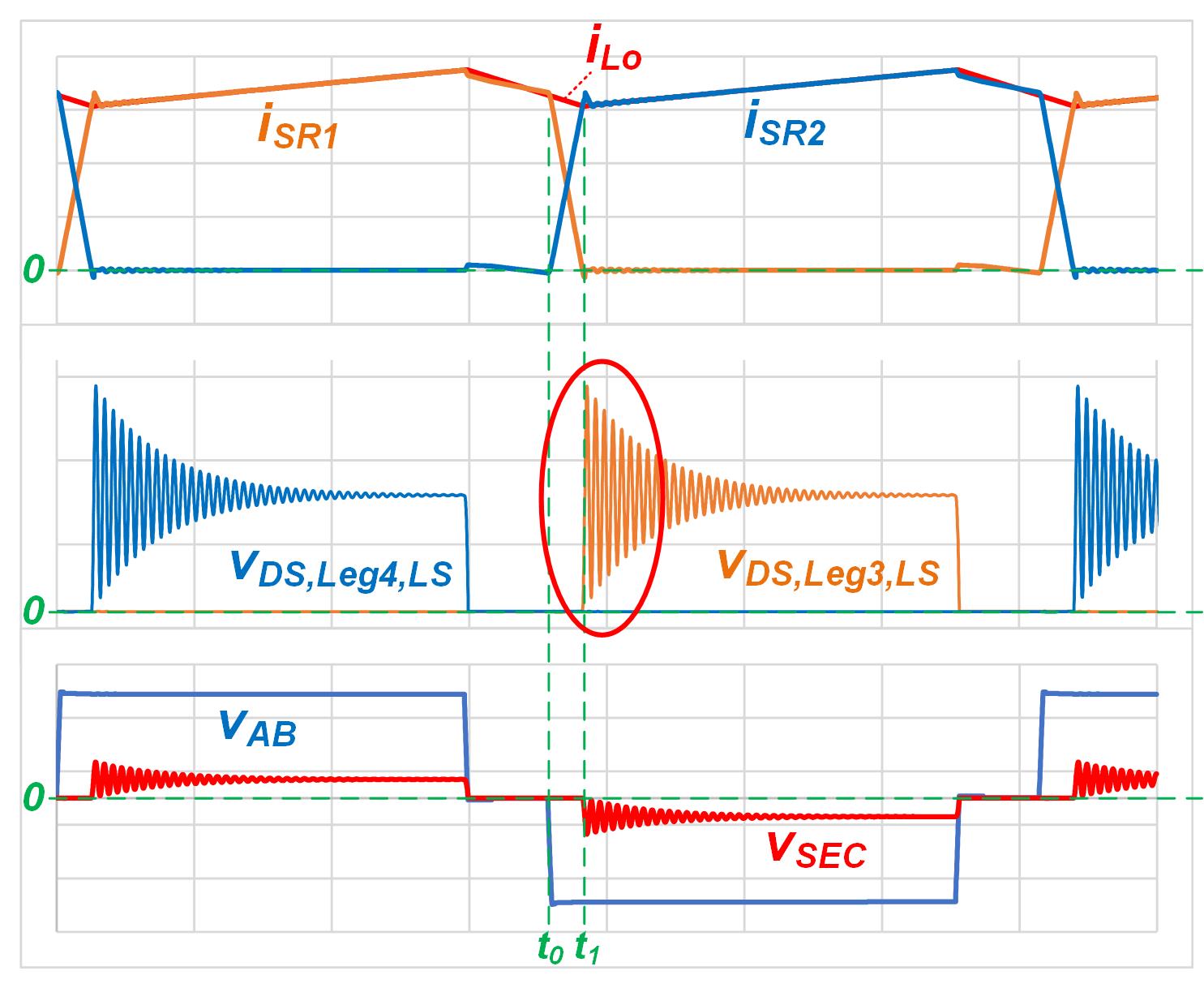

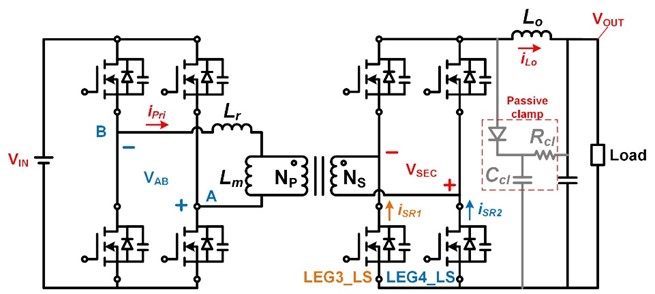

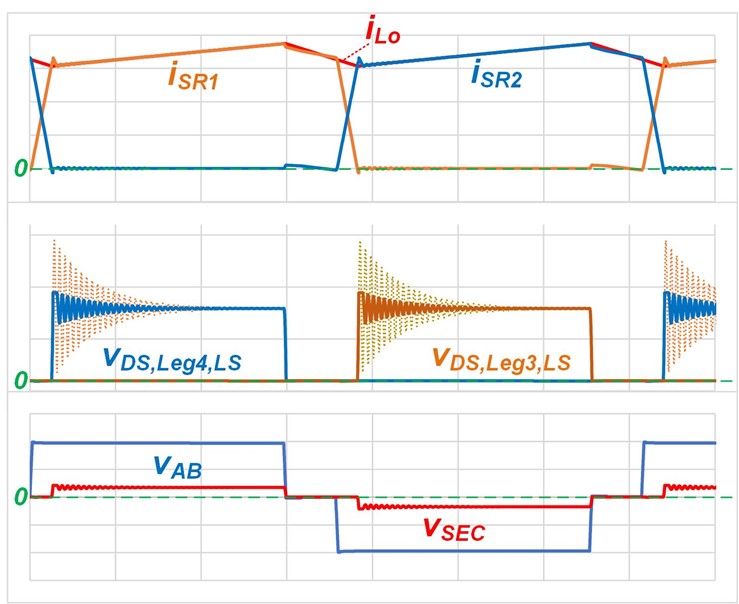

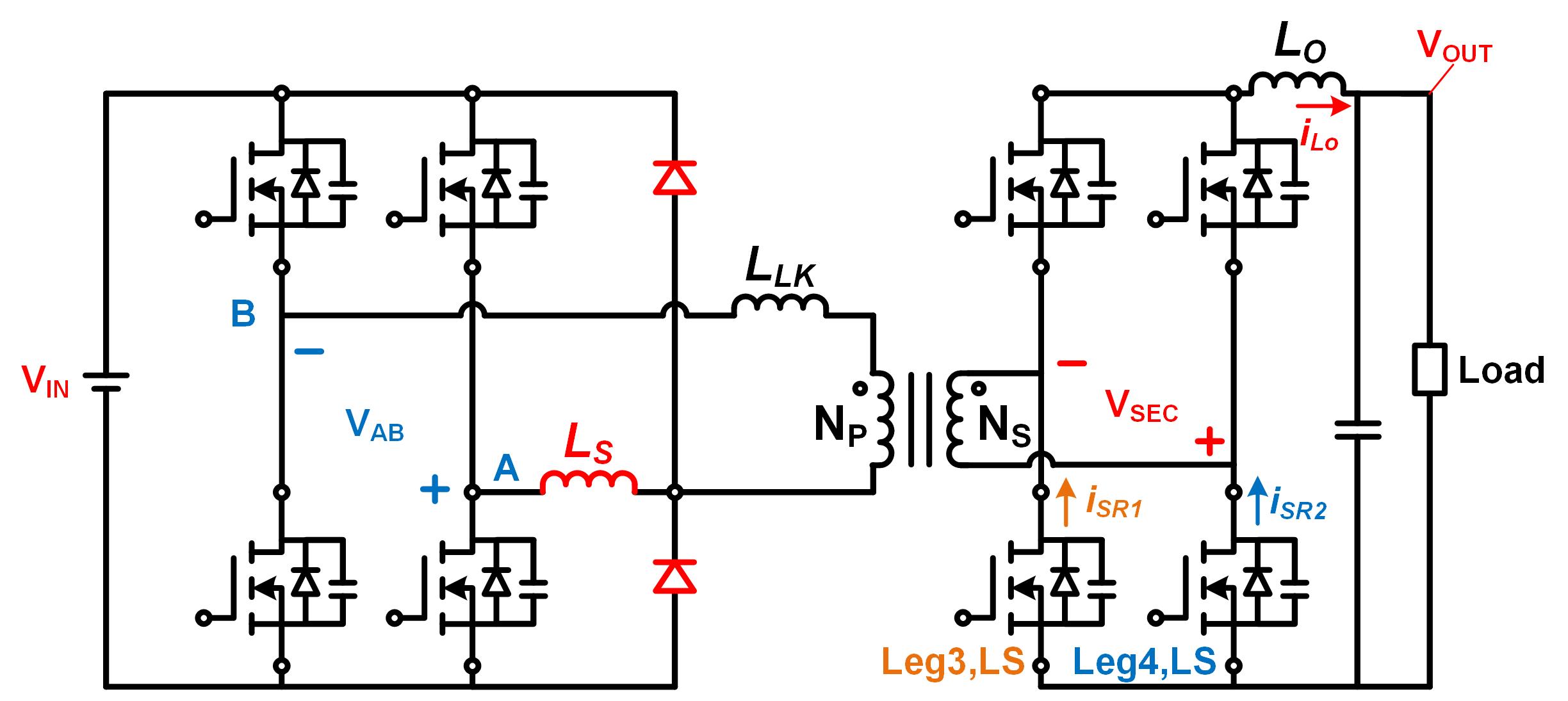

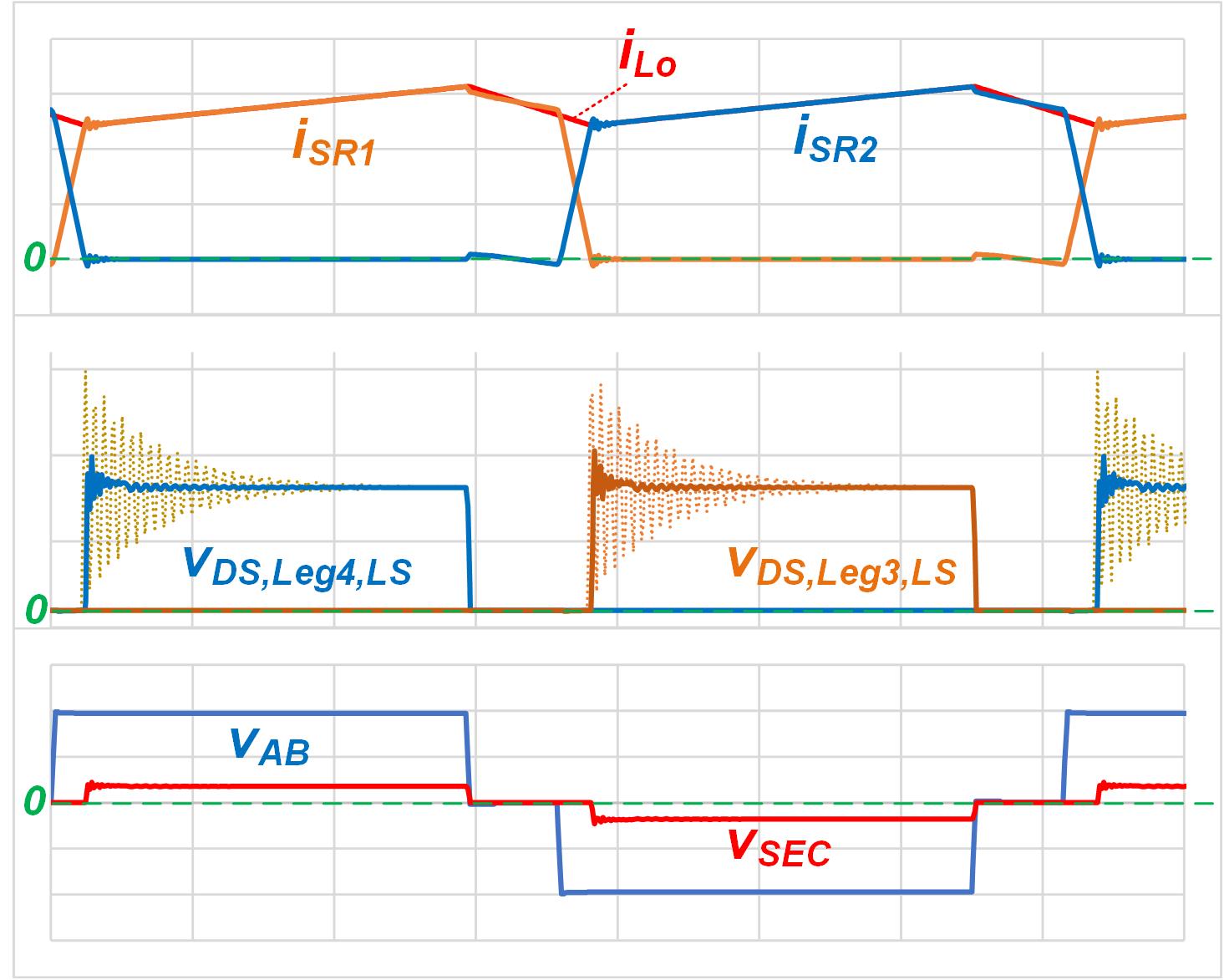

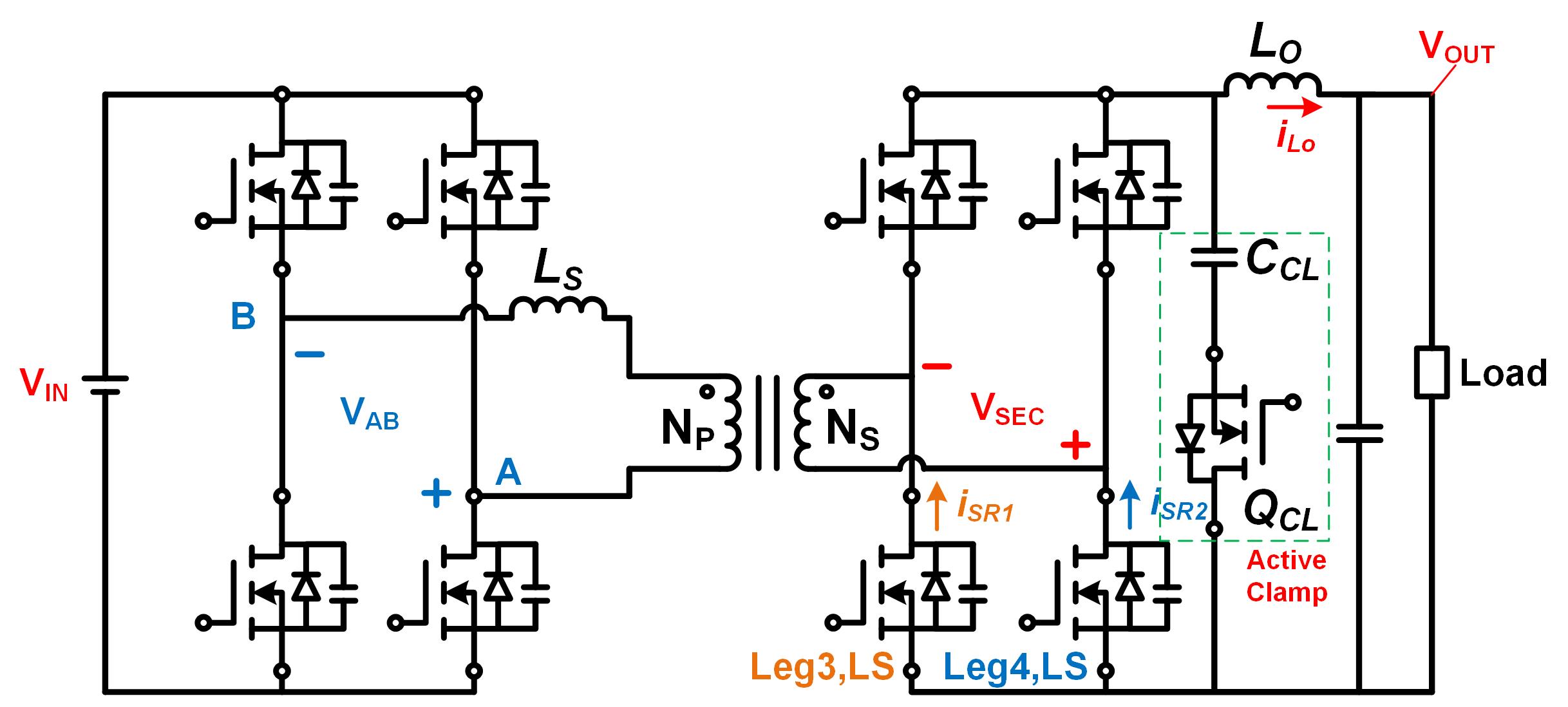

그림 18에 풀 브리지 동기 정류기가 있는 PSFB를 고려하십시오. 동기 정류기 VDS 전압은 그림 19에 나와 있는 것처럼 큰 링잉을 갖게 되며 FET 출력 커패시턴스가 모델링됩니다. 링잉의 피크 값은 2V IIN × NS/NP까지 높을 수 있습니다. 정류기 전압 응력을 줄이고 더 낮은 드레인-소스 온-저항(RDS(on)) FET를 사용하여 더 높은 효율을 위해서는 정류기 전압 응력을 클램핑해야 할 수 있습니다. 한 가지 옵션은 수동 클램프 회로를 적용하여 전압 링잉에서 부분 에너지를 흡수하는 것입니다. 그림 20에서는 PSFB에 적용되는 패시브 클램프 옵션을 보여줍니다. 그림 21에서는 출력 스테이지에 저항-커패시터 다이오드를 추가하여 정류기 전압 응력을 크게 줄이는 방법을 보여줍니다. 클램핑 커패시터(CCL)의 커패시턴스는 정류기 전압 응력을 효과적으로 클램핑하기 위한 이상적인 전압 소스로 취급할 수 있을 만큼 충분히 작아야 합니다. Ccl은 클램핑 다이오드에 의해 충전되고 Rcl에서 에너지를 소산합니다. 방정식 4는 대상 클램프 전압 레벨(VCP)에서 정류기 전압을 클램핑하는 데 필요한 클램핑 저항(Rcl) 저항을 계산합니다.

여기서 Vd = VIN × NS/NP와 fSW는 PSFB 스위칭 주파수입니다.

방정식 5는 클램핑 저항의 전력 손실을 계산하는 방법은 다음과 같습니다.

방정식 4와 방정식 5에서 볼 수 있듯이, 더 낮은 VCP는 Rcl에서 더 낮은 Rcl과 더 높은 전력 손실을 필요로 합니다.

그림 18 동기 정류기가 있는 PSFB.

그림 18 동기 정류기가 있는 PSFB. 그림 19 출력 정류기에서 전압 클램핑이 없는 PSFB의 파형.

그림 19 출력 정류기에서 전압 클램핑이 없는 PSFB의 파형. 그림 20 패시브 클램프가 있는 PSFB 컨버터.

그림 20 패시브 클램프가 있는 PSFB 컨버터. 그림 21 패시브 클램프 회로가 있는 PSFB의 파형(실선 포함).

그림 21 패시브 클램프 회로가 있는 PSFB의 파형(실선 포함).PSFB는 소프트 스위칭을 달성하기 위해 변압기 권선과 직렬로 연결된 인덕터에 저장된 에너지를 사용합니다. 그러나 인덕터는 정류기 기생 커패시터와 공명하여 높은 정류기 전압 응력을 만듭니다. 변압기 직렬 인덕터의 인덕턴스를 줄일 수 있으면 정류기 전압 강도를 줄일 수 있습니다. 그림 22에 나와 있는 1차 클램프는 하프 브리지 FET 레그와 클램핑 다이오드 사이에 변압기 시리즈 인덕터를 배치한 두 개의 다이오드를 추가하여 더 작은 직렬 인덕터를 사용할 수 있습니다. 이렇게 하면 유일한 변압기 직렬 인덕터는 변압기 누설 인덕터가 됩니다.

그림 23에는 1차 클램프 사용 여부와 관계없이 PSFB의 파형이 나와 있습니다. LS는 3.5µH로 설정되며 누설 인덕턴스(Llk)는 0.5µH로 설정됩니다. 다이오드 클램프가 1차측에 있기 때문에 LS로 에너지를 재활용해서 1차측에 유지할 수 있습니다. 출력 정류기 기생 커패시터는 Llk에만 공명하여 출력 정류기 전압 응력을 크게 줄입니다. 작은 Llk로 소프트 스위칭을 유지하기 위해 1차 클램프가 있는 PSFB의 개별 인덕터 LS가 필요하기 때문에, 다른 클램핑 방법을 사용할 경우 전력 밀도가 PSFB보다 낮을 수 있습니다.

그림 22 1차측 클램프가 있는 PSFB 컨버터.

그림 22 1차측 클램프가 있는 PSFB 컨버터. 그림 23 1차측 클램프 회로가 있는 경우(실선)와 없는 경우(점선)의 PSFB 파형.

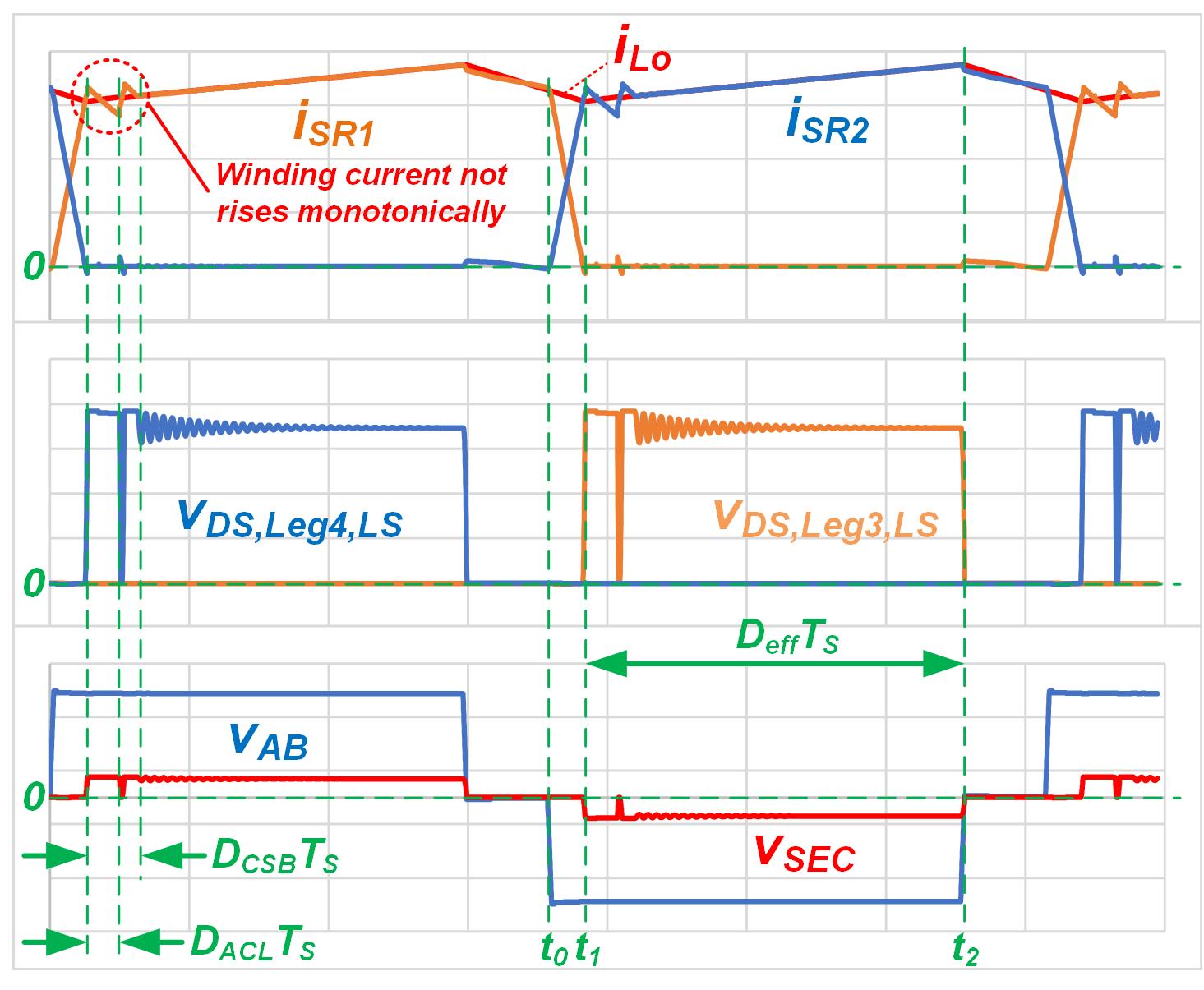

그림 23 1차측 클램프 회로가 있는 경우(실선)와 없는 경우(점선)의 PSFB 파형.패시브 클램프와 같은 클램프 저항의 전력을 연소하거나 기본 클램프와 같은 개별 인덕터를 추가하는 대신, 그림 24에 표시된 액티브 클램프를 사용하면 크기와 효율성을 모두 최적화하는 데 도움이 될 수 있습니다. 커패시터(CCL)와 MOSFET(QCL)에 의해 형성된 액티브 클램프 레그(ACL)는 출력 인덕터 전에 삽입됩니다. 출력 권선 전압이 nonzero가 되면, 전력이 1차 권선에서 2차 권선으로 옮겨가면서 QCL 전원이 켜져 있지 않더라도 CCL을 충전하기 위해 QCL 본체 다이오드를 통해 출력 인덕터에 전력을 공급하고 전류를 전도하게 됩니다. 본체가 이미 전류를 전도한 후에 QCL 전원을 켜면 QCL에서 ZVS(제로 전압 스위칭)를 보장할 수 있습니다. DeffTS 시작 시 CCL에서 전류 초 균형(또는 전하 균형)을 완료할 수 있도록 전류 극성 변경 전에 QCL을 켜는 것이 중요합니다.

그림 25은 동기 정류기 전류와 변압기 권선 전류에 비단조 전류가 있음을 보여주며, 피크 전류 모드 제어는 일반적으로 유효 듀티 사이클 기간 동안 변압기 전류에 단조 전류 상승이 필요하므로 피크 전류 모드 제어에 문제가 될 수 있습니다. QCL은 액티브 클램프 전류 초 균형이 의도한 대로 작동하여 출력 정류기 전압을 CCL 전압(VCL)에 클램핑할 수 있을 만큼만 켜두면 됩니다. QCL은 전체 DeffTS 전체에 걸쳐 수행할 필요가 없지만 상대적으로 짧은 시간 동안 수행할 수 있습니다.

따라서 전체 작동 전압 및 부하 범위에서 전류-초 균형이 완료되는 기간(DCSBTS)보다 항상 큰 DeffTS를 유지하면서 QCL이 고정 온 시간(DACLTS = 상수)을 갖도록 설정할 것을 제안합니다. DeffTS는 DCSBTS보다 크므로 변압기 전류가 단조롭게 상승할 때 피크 전류 감지가 항상 발생합니다. PSFB는 일반적으로 Deff >> DCSB가 예상되는 중간 부하에서 무거운 부하까지 더 큰 Deff를 갖도록 설계되었습니다. 경부하에서 컨버터는 대개 불연속 전도 모드에서 작동하며, 이 모드에서 Deff는 입력/출력 전압 조건이 같을 때 연속 보드 하에서의 Deff보다 더 작습니다.

경부하에서도 DeffTS를 DCSBTS보다 더 크게 유지하기 위해 주파수 감소 제어 또는 버스트 작동을 구현할 수 있습니다. 듀티 사이클 손실 기간이 끝난 후에만 QCL을 켜는 것이 중요합니다. 그렇지 않으면 CCL에 저장된 에너지가 1차측으로 다시 덤프되고, 동기 정류기를 오버스트레스하고, 부품에 손상을 줄 수 있습니다. CCL은 동기 정류기 전압 응력을 효과적으로 줄이기 위한 이상적인 전압 소스로 취급할 수 있을 만큼 충분히 작아야 합니다. 따라서 CCL 선택이 방정식 6로 표현되는 부등성을 충족하도록 해야 합니다.

CCL에서 제로 전압 리플을 가정할 경우 정류기 전압을 VINNS/NP로 클램핑할 수 있으며, 이는 클램프 회로 없이 전압 응력의 절반입니다. 액티브 클램프는 전원 저항의 링잉 에너지를 소모하지 않지만 무손실 스너버로 LC 공진 탱크의 에너지를 순환합니다. 따라서 동일한 사양에서 패시브 클램프를 적용한 PSFB에 비해 액티브 클램프를 적용한 PSFB에서 더 높은 컨버터 효율을 기대할 수 있습니다.

동기 정류기 COSS는 ACL의 피크 전류를 제어합니다. 낮은 COSS 동기 정류기 FET를 선택하면 ACL RMS(루트 평균 제곱) 전류가 더 낮으므로 컨버터 효율을 개선하는 데 도움이 됩니다.

다음은 액티브 클램프가 있는 PSFB를 설계할 때 사용할 수 있는 몇 가지 설계 지침입니다.

- QCL은 CCL 전류가 1차측으로 역류하는 것을 방지하려면 반드시 듀티 사이클 손실 기간 이후에 전원을 켜야 합니다.

- QCL은 바디 다이오드가 ZVS에 아직 전류를 전도하고 있는 동안은 계속 켠 상태를 유지해야 합니다.

- QCL 온타임이 길어질수록 VCL과 동기 정류기 전압 스트레스가 감소하지만 QCL RMS 전류는 증가합니다.

- 낮은 동기 정류기 COSS는 ACL RMS 전류를 줄이는 데 도움이 될 뿐만 아니라 동기 정류기 전압 응력을 줄이는 데 도움이 됩니다.

그림 24 액티브 클램프를 적용한 PSFB.

그림 24 액티브 클램프를 적용한 PSFB. 그림 25 패시브 클램프를 적용한 PSFB의 파형.

그림 25 패시브 클램프를 적용한 PSFB의 파형.