KOKP007 April 2024

2 PSFB 작동 원리

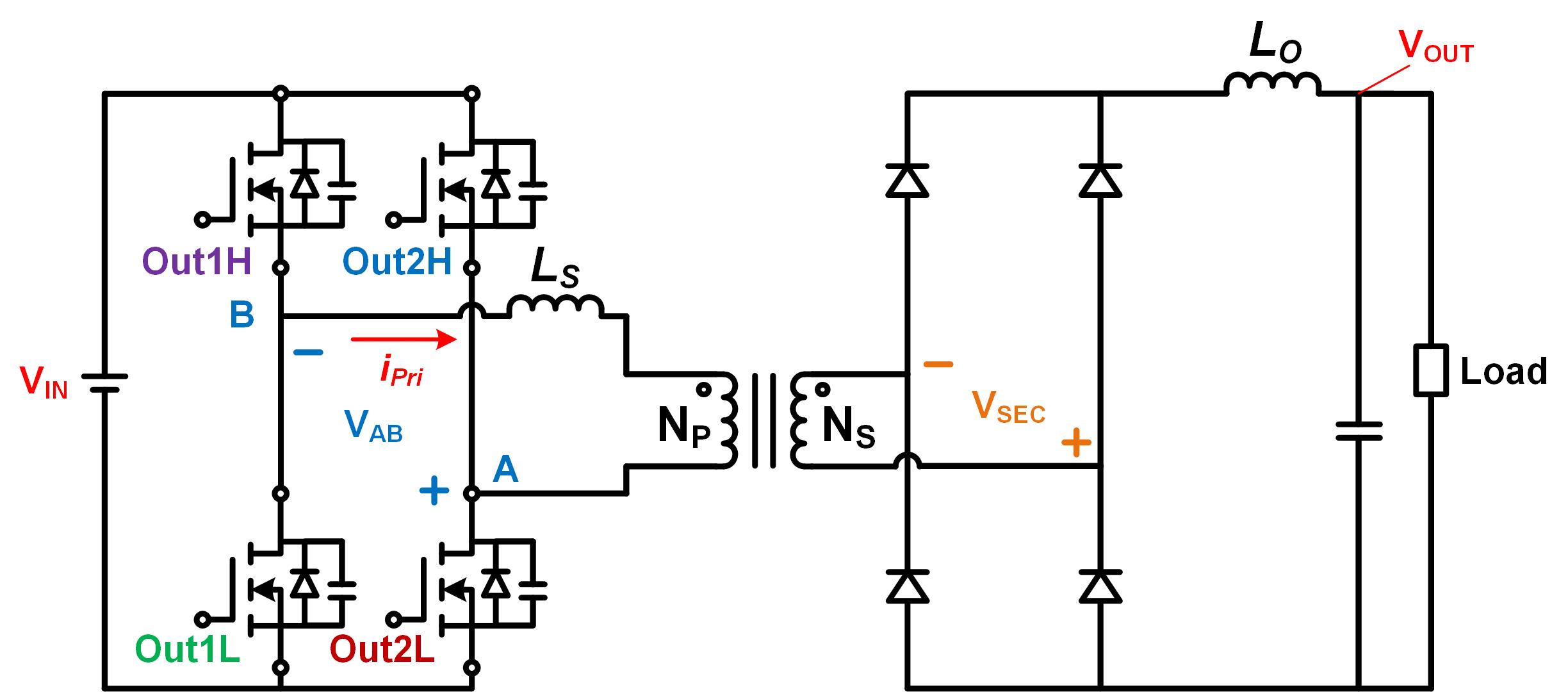

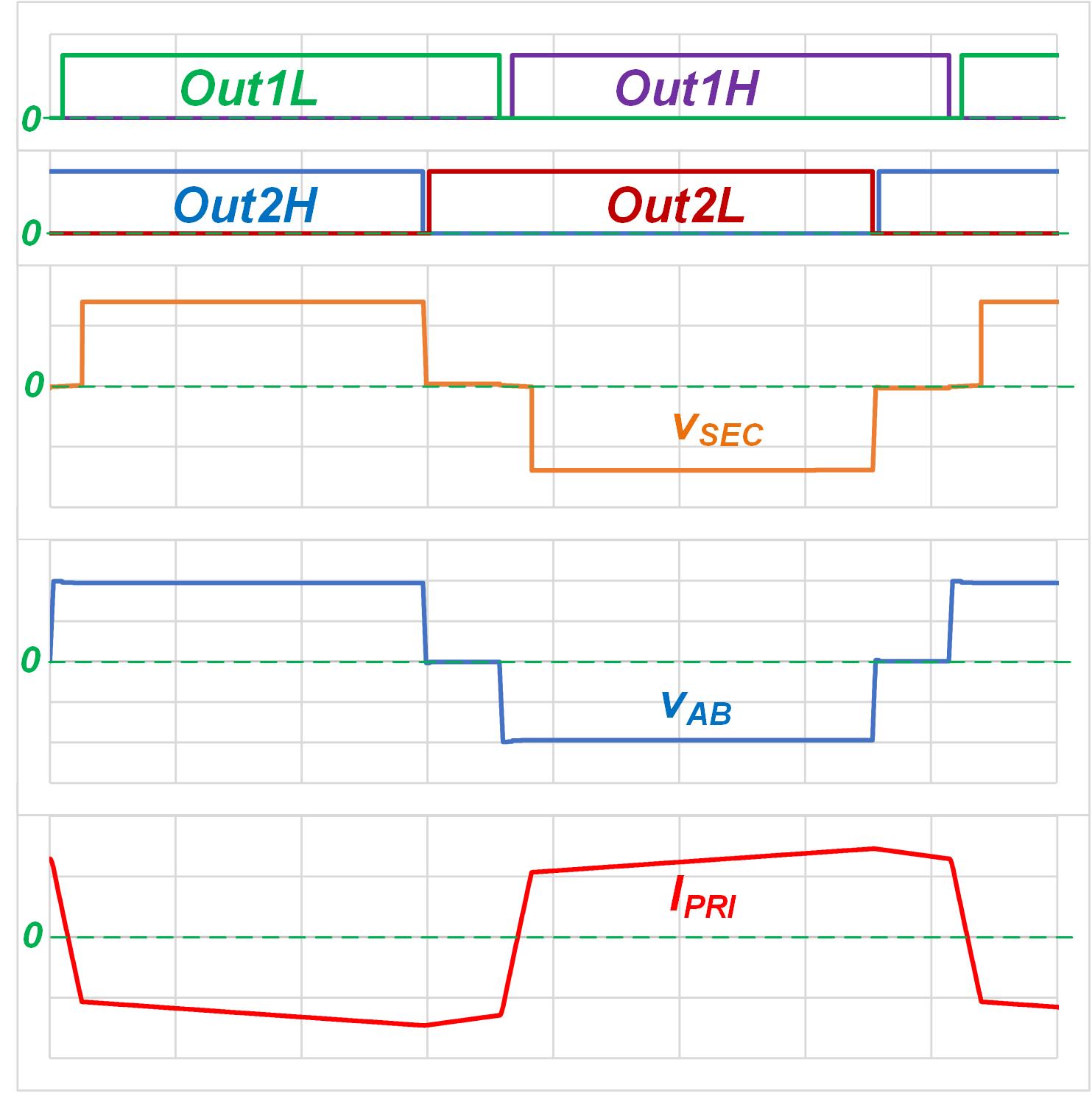

그림 9은 다이오드 정류기가 있는 풀 브리지 컨버터를 보여주며, 그림 10은 위상 전환 제어 하에서 풀 브리지 컨버터 파형을 보여줍니다. 이를 통해 MOSFET가 소프트 스위칭에 대해 과도현상으로 켜지기 전에 음극 드레인-소스 전류를 구현할 수 있습니다. 그림 10에서 보듯이 레그 1 MOSFET 구동 신호(Out1L 및 Out1H)와 레그 2 MOSFET 구동 신호(Out2L 및 Out2H) 사이에 위상 차이가 만들어지지만, 4개의 구동 신호 모두 듀티 사이클은 변함없이 유지됩니다. MOSFET 대각선 쌍이 켜지면 입력 전압(+VIN) 또는 역변환 입력 전압(–VIN)이 VAB에 적용되고 이는 직렬 인덕터(LS)가 통전되고 변압기를 통해 입력 측(1차측)에서 출력 측(2차측)으로 에너지가 전달되기까지의 시간입니다. 레그 1과 레그 2 사이의 위상 차이는 VAB의 0이 아닌 전압 지속 시간(펄스 폭)을 결정합니다. VAB 파형과 유사한 양극 사각파가 2차 전압(VSEC)에서 생성됩니다. 이는 출력 다이오드 정류기에서 추가 정류되어 단극 구형이 되기 때문에 출력 인덕터가 VSEC 펄스 폭에 의해 제어되는 출력 조정을 위한 "벅" 작동을 수행할 수 있습니다.

그림 9 풀 브리지 정류기가 있는 PSFB.

그림 9 풀 브리지 정류기가 있는 PSFB. 그림 10 PSFB 파형.

그림 10 PSFB 파형.LS가 적용된 VIN을 사용하여 전류 극성을 전환하기 때문에 VSEC의 펄스 너비가 VAB보다 작습니다. 그 결과 변압기 권선에서 전압이 0이므로 듀티 사이클 손실이라고 하는 VSEC 펄스 너비가 작아집니다. LS 인덕턴스가 클수록 듀티 사이클 손실이 커집니다(VAB와 VSEC 간의 펄스 폭 차이). 더 넓은 듀티 사이클 변이 범위를 위해 2차측에서 더 큰 Deff를 구현하려면 더 작은 LS 인덕턴스를 사용해야 합니다.

스위칭 과도 상태에서 LS에 저장된 에너지는 1차측 MOSFET에서 소프트 스위칭을 실현하는 데 있어 핵심입니다. LS 인덕턴스가 작으면 저장된 에너지가 적다는 것으로, 특히 저부하에서 소프트 스위칭을 위해 MOSFET 출력 커패시터 전압을 방전하기에 충분하지 않을 수 있습니다. 따라서 설계에서 소프트 스위칭과 Deff 범위 간에 절충이 있어야 합니다.

위상 전환 제어는 1차 권선 전류가 1차 풀 브리지 MOSFET의 COSS 및 바디 다이오드를 통해 지속적으로 순환하고 자유롭게 흐르게 할 수 있도록 하기 때문에 이전에 그림 8에서 보듯이 풀 브리지 스위치 노드의 출력에서 유도 임피던스를 갖는 MOSFET에 전류 지연, MOSFET 스위칭 과도 상태에서 음극 전류가 발생할 수 있습니다. LS에 저장된 에너지는 소프트 스위칭의 핵심이지만 출력 인덕터 LO는 소프트 스위칭 기능도 영향을 줍니다.

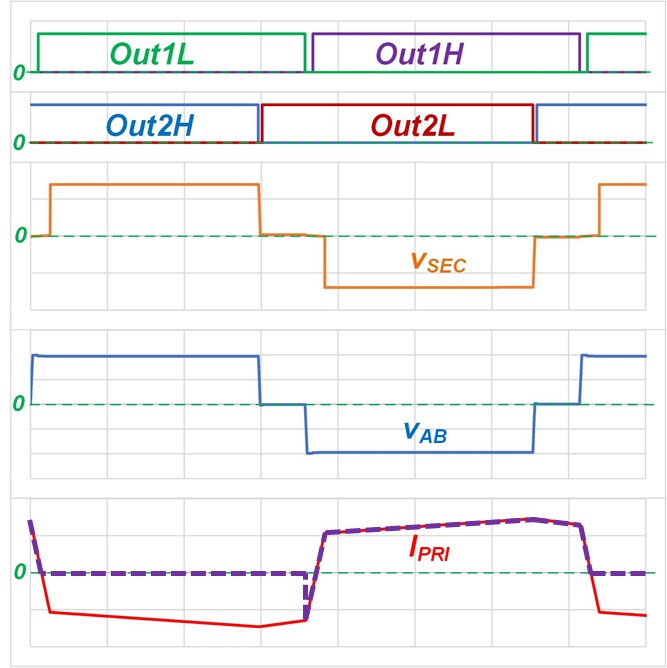

MOSFET 스위칭 트랜션트의 파형을 살펴보겠습니다. 의그림 11 파선 보라색 곡선은 레그 1 고압측 MOSFET 전류입니다. 레그 1 저압측 MOSFET 전류는 레그 1 고압측 MOSFET 전류와 동일하지만 레그 1 고압측 MOSFET 턴오프 기간에 발생한다는 것을 알 수 있습니다. MOSFET 시동 과도 상태의 1차 전류(IPRI) 레벨이 LO 전류 리플 밸리 포인트에 있다는 것을 알 수 있습니다. 즉, LO 전류 리플이 크면(즉 LO 인덕턴스가 더 작으면) 레그 1 MOSFET의 소프트 스위칭 기능이 떨어집니다. 변압기 자화 인덕터 전류가 0이라고 가정하면 방정식 2는 레그 1 MOSFET에서 소프트 스위칭을 달성하는 데 사용되는 전류를 다음과 같이 표현합니다.

여기서I LO, pp는 LO의 피크-대-피크 전류 리플입니다.

방정식 3에서는 레그 2 MOSFET에서 소프트 스위칭을 달성하는 데 사용되는 전류를 다음과 같이 계산합니다.

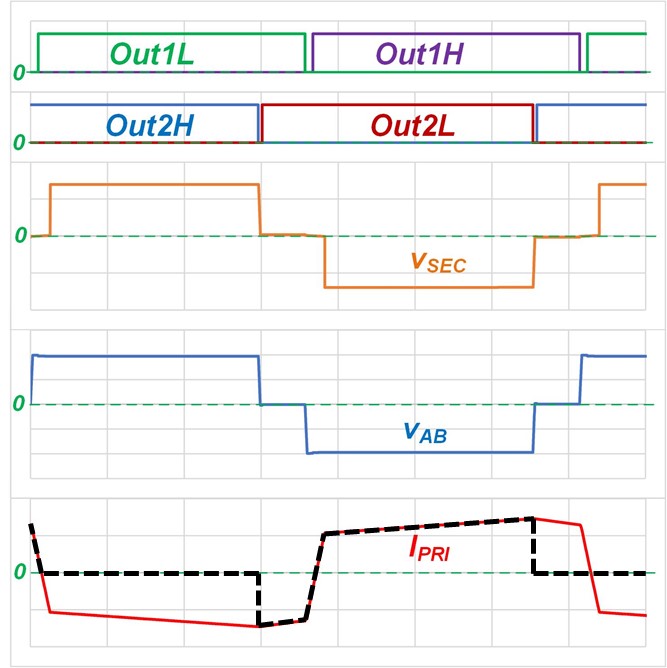

그림 12는 레그 2 저압측 MOSFET 전류를 검은색 파선으로 표시한 것입니다. 레그 2 고압측 MOSFET 전류는 레그 2 저압측 MOSFET 전류와 동일하지만 레그 2 저압측 MOSFET 턴오프 기간에 발생한다는 것을 알 수 있습니다. 방정식 2 및 방정식 3에서 그리고 그림 11 및 그림 12의 파형과 함께 레그 1보다 레그 2에서 MOSFET의 소프트 스위칭을 달성하는 것이 더 편하다는 것을 알 수 있습니다.

그림 11 레그 1 고압측 MOSFET 전류를 보라색 파선으로 강조 표시하는 PSFB 파형.

그림 11 레그 1 고압측 MOSFET 전류를 보라색 파선으로 강조 표시하는 PSFB 파형. 그림 12 레그 2 저압측 MOSFET 전류를 검은색 파선으로 강조 표시하는 PSFB 파형.

그림 12 레그 2 저압측 MOSFET 전류를 검은색 파선으로 강조 표시하는 PSFB 파형.